Prepare Modules

$ mkdir fir$ cd fir

Copy this example application: fir.c

Copy this input file: fir_input.dat

$ c2mod.py fir.c

Module "tap1" created with 1 input(s) and 2 output(s).

Module "tap2" created with 1 input(s) and 2 output(s).

Module "tap3" created with 1 input(s) and 2 output(s).

Module "tap4" created with 1 input(s) and 2 output(s).

Module "tap5" created with 1 input(s) and 1 output(s).

Module "add" created with 5 input(s) and 1 output(s).

Total 6 module(s) created.

Copy these modules to the AsapMap modules folder

$ cp *.mod /net/pizza/vcl/lib/asapmap/modules/

TIP: put this in your .cshrc file in your home folder:

alias copymod 'cp *.mod /net/pizza/vcl/lib/asapmap/modules/'

then just use the command copymod each time you want to copy over the modules.

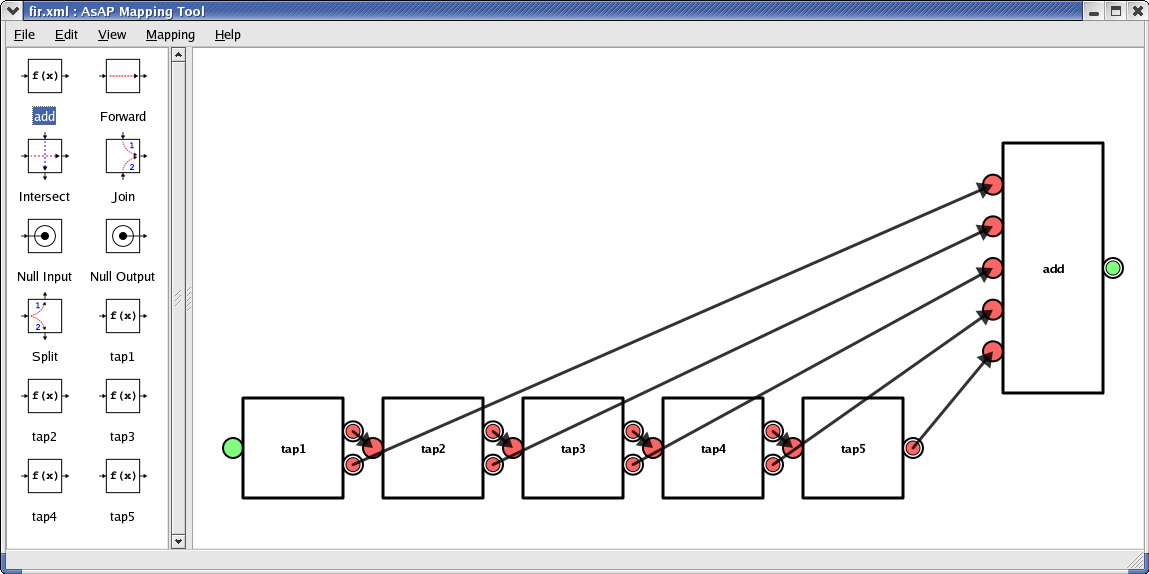

Create Application

$ asapmapCreate this simple application

Save the application to XML file (File -> Save As...)

Name the output file as fir.xml

Simulate Output

$ runptsim.py fir.ctest_gen: finished scanning all of input

test_read: finished writing all of output

application called MPI_Abort(MPI_COMM_WORLD, 0) - process 3,

[mpiexec@pepper] ONE OF THE PROCESSES TERMINATED BADLY: CLEANING UP

APPLICATION TERMINATED WITH THE EXIT STRING: Terminated (signal 15)

This error message is normal and is a result of the program exiting through the use of an 'abort' command.

You can compare your output with the data in chip_output_data.m

VCL | ECE Dept. | UC Davis Last update: September 7, 2011