### A FINE GRAINED MANY-CORE H.264 VIDEO ENCODER

By

STEPHEN THE UY LE B.S. (Oregon State University) March, 2007

#### THESIS

Submitted in partial satisfaction of the requirements for the degree of

MASTER OF SCIENCE

in

Electrical and Computer Engineering

in the

#### OFFICE OF GRADUATE STUDIES

of the

#### UNIVERSITY OF CALIFORNIA

DAVIS

Approved:

Chair, Dr. Bevan M. Baas

Member, Dr. Venkatesh Akella

Member, Dr. Soheil Ghiasi

Committee in charge 2010

© Copyright by Stephen The Uy Le 2010 All Rights Reserved

### Abstract

Video encoding has become an integral part for everyday computing from televisions and computers to portable devices such as cell phones. Achieving high quality resolution over limited bandwidth has lead to the development of the H.264 video standard providing greater encoding performance. In this work an H.264 baseline video encoder is presented on a fine grained 167-core programmable processor allowing for greater flexibility and parallelization. The encoder presented is capable of encoding QCIF-resolution video at 1.00 GHz while dissipating an average of 438 mW, and CIF-resolution at 1.20 GHz while an average of 787 mW. The Asynchronous Array of Simple Processors (AsAP) platforms provides a new method of coding over a large number of simple processors allowing for a higher level of parallelization than digital signal processors (DSP) while avoiding the complexity of a fully application specific integrated circuit (ASIC).

### Acknowledgments

I would like to take this chance to thank to everyone that made this work possible. First I would like to thank Professor Baas for his time, guidance, and support throughout my years at Davis. The lessons that I learned here will help me for the rest of my career. I would like to thank Professor Akella and Professor Ghiasi for their valuable support and time in reviewing my thesis.

Thank you to the University of California Davis for providing this educational institution for learning and enrichment. Graduate school has opened many more doors for me in the future.

I would also like to thank Zhibin Xiao and Gouri Landge for their previous work on video encoding and Dean Truong for helping me work on the AsAP chip, without your help it would have taken me much longer to complete this project. I would also like to thank Henna Huang, Layne Miao and all of the members of the VCL lab for their help and support throughout my project making it not only a great learning experience but a great place to work.

Lastly I would like to thank my family. To my wife and daughter who put up with me during these long months, thank you for your support and understanding on those 70+ hours of work a week. Thank you to my parents and siblings for their encouragement and support throughout this time.

This work was supported by ST Microelectronics; IntellaSys; SRC GRC Grant 1598 and CSR Grant 1659; UC Micro; NSF Grant 0430090, CAREER Award 0546907 and Grant 0903549; Intel; and SEM. Any opinions, findings, and conclusions or recommendations expressed in this material are those of the author and do not necessarily relect the views of the National Science Foundation or any of the sponsors.

# Contents

| Ab  | Abstract ii         |               |                                                            |    |  |  |  |  |  |

|-----|---------------------|---------------|------------------------------------------------------------|----|--|--|--|--|--|

| Ac  | Acknowledgments iii |               |                                                            |    |  |  |  |  |  |

| Lis | List of Figures vii |               |                                                            |    |  |  |  |  |  |

| Lis | st of ]             | <b>[ables</b> |                                                            | X  |  |  |  |  |  |

| 1   | Intro               | Introduction  |                                                            |    |  |  |  |  |  |

|     | 1.1                 | Goals of      | of Parallel Video Encoding                                 | 1  |  |  |  |  |  |

|     | 1.2                 | Project       | Contributions                                              | 1  |  |  |  |  |  |

|     | 1.3                 | Organi        | zation                                                     | 2  |  |  |  |  |  |

| 2   | Over                | rview of      | Video Encoding and the H.264 Standard                      | 3  |  |  |  |  |  |

|     | 2.1                 | Genera        | l Video Encoding Concepts                                  | 3  |  |  |  |  |  |

|     |                     | 2.1.1         | Digital Video                                              | 4  |  |  |  |  |  |

|     |                     | 2.1.2         | Video Format                                               | 5  |  |  |  |  |  |

|     |                     | 2.1.3         | Macroblock Partitioning                                    | 7  |  |  |  |  |  |

|     |                     | 2.1.4         | Encoding Motion                                            | 7  |  |  |  |  |  |

|     | 2.2                 | Overvi        | ew of H.264                                                | 10 |  |  |  |  |  |

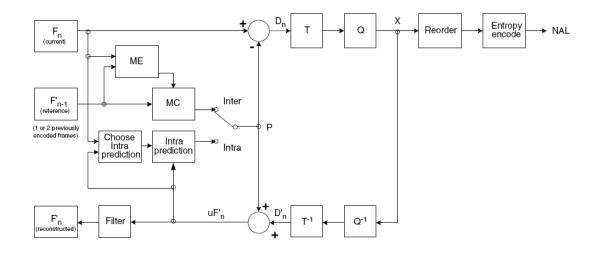

|     |                     | 2.2.1         | Encoding Path                                              | 11 |  |  |  |  |  |

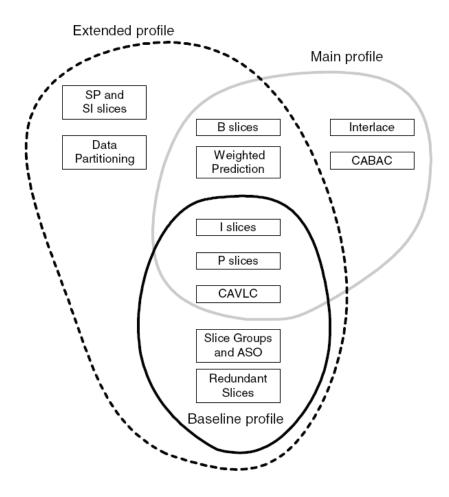

|     |                     | 2.2.2         | Profiles                                                   | 12 |  |  |  |  |  |

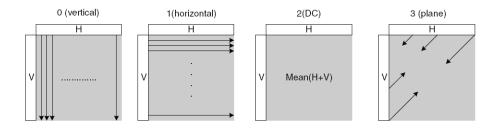

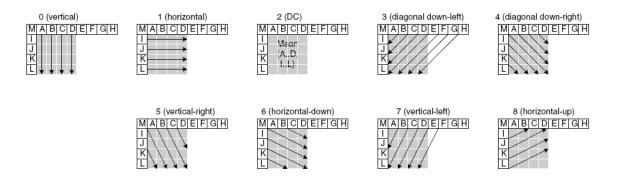

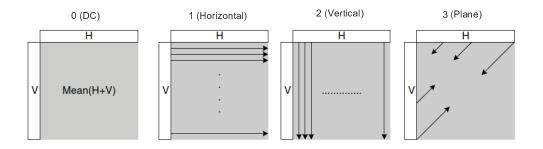

|     |                     | 2.2.3         | Intra Prediction                                           | 12 |  |  |  |  |  |

|     |                     | 2.2.4         | Inter Prediction                                           | 16 |  |  |  |  |  |

|     |                     | 2.2.5         | Integer Transform and Quantization                         | 18 |  |  |  |  |  |

|     |                     | 2.2.6         | Reference Frame Reconstruction                             | 23 |  |  |  |  |  |

|     |                     | 2.2.7         | Entropy Coding                                             | 23 |  |  |  |  |  |

|     |                     | 2.2.8         | Network Abstraction Layer                                  | 27 |  |  |  |  |  |

| 3   | Proc                | essing I      | Platforms Used for Video Encoding                          | 31 |  |  |  |  |  |

|     | 3.1                 | Related       | d Work in H.264 Processing                                 | 31 |  |  |  |  |  |

|     |                     | 3.1.1         | Video Encoding on General Purpose (GP) Processors          | 32 |  |  |  |  |  |

|     |                     | 3.1.2         | Video Encoding on Digital Signal Processors (DSP)          | 32 |  |  |  |  |  |

|     |                     | 3.1.3         | Video Encoding on Application Specific Integrated Circuits | 33 |  |  |  |  |  |

|     | 3.2                 | Propos        | ed H.264 Video Encoder Platform                            | 33 |  |  |  |  |  |

|     |                     | 3.2.1         | General Overview of AsAP2 Architecture                     | 33 |  |  |  |  |  |

|     |                     | 3.2.2         | Dynamic Voltage and Frequency Scaling (DVFS)               | 34 |  |  |  |  |  |

|   |      | 3.2.3          | Memory Architecture                               |   |   |     | • |   |   |   |   | 35       |

|---|------|----------------|---------------------------------------------------|---|---|-----|---|---|---|---|---|----------|

|   |      | 3.2.4          | Processor Interconnect                            |   |   |     |   |   |   |   |   | 35       |

|   |      | 3.2.5          | Motion Estimation Accelerator                     | • |   |     |   | • |   | • | • | 35       |

| 4 | Para | allel Pro      | ogramming Tools                                   |   |   |     |   |   |   |   |   | 41       |

|   | 4.1  | Messa          | ge Passing Interface (MPI)                        |   |   |     |   |   |   |   |   | 41       |

|   |      | 4.1.1          | Parallel C/MPI Wrapper                            |   |   |     |   |   |   |   |   | 41       |

|   |      | 4.1.2          | AsAP Arbitrary Mapping Tool                       |   |   |     |   |   |   |   |   | 42       |

|   | 4.2  | Paralle        | el Programming                                    |   |   |     | • |   |   |   |   | 45       |

|   |      | 4.2.1          | Methodology                                       |   |   |     |   |   |   |   |   | 45       |

|   |      | 4.2.2          | Pitfalls                                          |   | • |     | • |   | • | • |   | 49       |

| 5 | Imp  | lementa        | ation                                             |   |   |     |   |   |   |   |   | 53       |

| · | 5.1  |                | el C Implementation                               |   |   |     |   |   |   |   |   | 53       |

|   | 0.1  | 5.1.1          | General Overview                                  |   |   |     |   |   |   |   |   | 53       |

|   |      | 5.1.2          | Intra Prediction                                  |   |   |     |   |   |   |   |   | 54       |

|   |      | 5.1.2          | Inter Prediction                                  |   |   |     |   |   |   |   |   | 54       |

|   |      | 5.1.4          | Integer Transform & Quantization & Entropy Coding |   |   |     |   |   |   |   |   | 55       |

|   |      | 5.1.4          | Network Abstraction Layer (NAL)                   |   |   |     |   |   |   |   |   | 55       |

|   |      | 5.1.6          | Reference Frame Reconstruction                    |   |   |     |   |   |   |   |   | 55       |

|   | 5.2  |                |                                                   |   |   |     |   |   |   |   |   | 56       |

|   | 5.2  | 5.2.1          | General Overview                                  |   |   |     |   |   |   |   |   | 56       |

|   |      | 5.2.1          | Memory Organization                               |   |   |     |   |   |   |   |   | 58       |

|   |      | 5.2.2          |                                                   |   |   |     |   |   |   |   |   | 58<br>62 |

|   |      | 5.2.5<br>5.2.4 | Control Logic    Intra Prediction                 |   |   |     |   |   |   |   |   | 64       |

|   |      | 5.2.4          |                                                   |   |   |     |   |   |   |   |   | 66       |

|   |      |                | Inter Prediction                                  |   |   |     |   |   |   |   |   |          |

|   |      | 5.2.6          | Integer Transform & Quantization & Entropy Coding |   |   |     |   |   |   |   |   | 70       |

|   |      | 5.2.7          | Network Abstraction Layer (NAL)                   |   |   |     |   |   |   |   |   | 73       |

|   |      | 5.2.8          | Reference Frame Reconstruction                    | • | • |     | • | • | · | • | • | 73       |

| 6 |      |                | l Analysis                                        |   |   |     |   |   |   |   |   | 77       |

|   | 6.1  |                | cs for Testing and Analysis                       |   |   |     |   |   |   |   |   | 77       |

|   | 6.2  |                | mance Comparisons                                 |   |   |     |   |   |   |   |   | 79       |

|   | 6.3  | •              | sis                                               |   |   |     |   |   |   |   |   | 82       |

|   |      | 6.3.1          | Chip Utilization                                  |   |   |     |   |   |   |   |   | 82       |

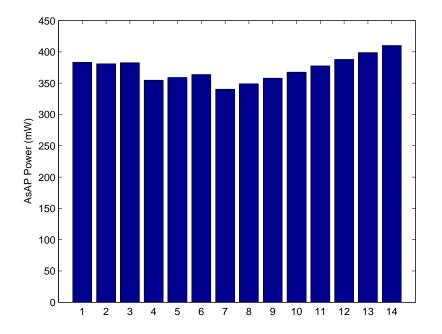

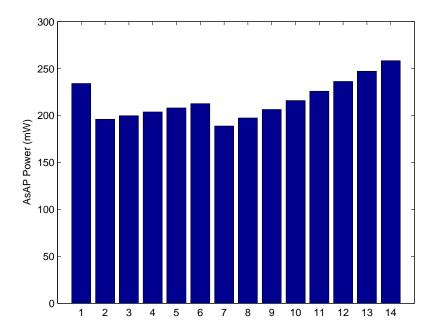

|   |      | 6.3.2          | Processor Energy                                  |   |   |     |   |   |   |   |   | 82       |

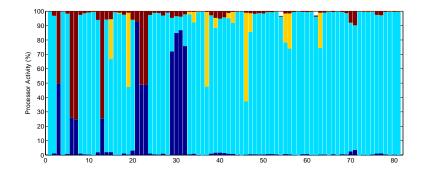

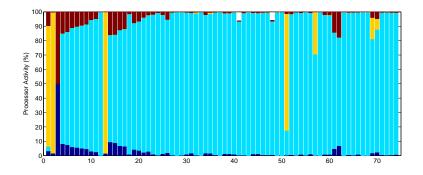

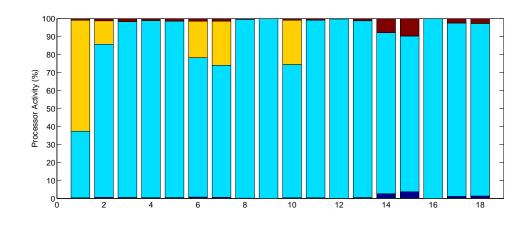

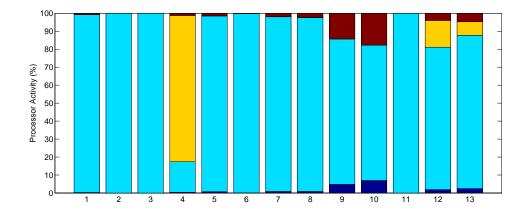

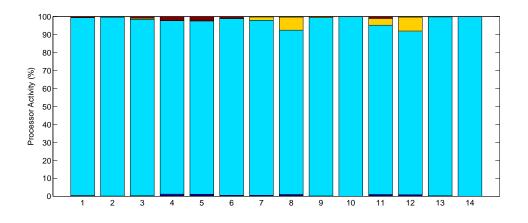

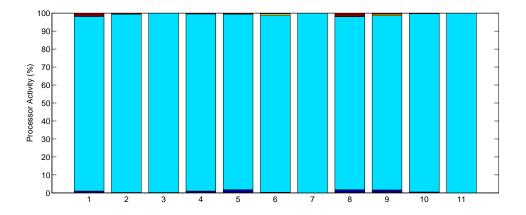

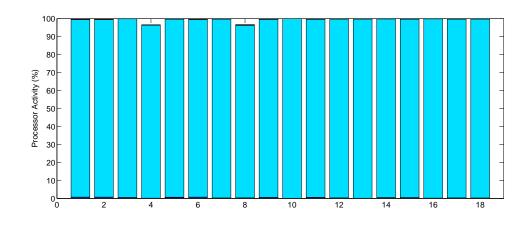

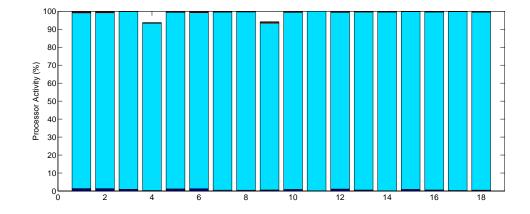

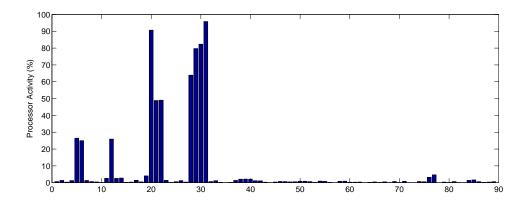

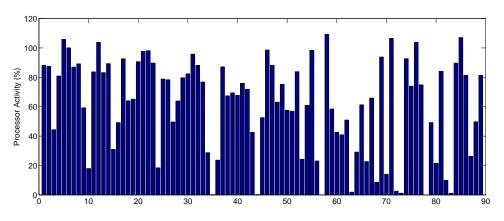

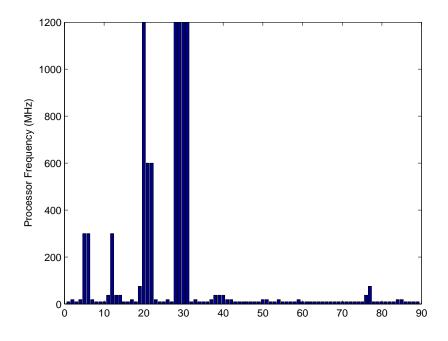

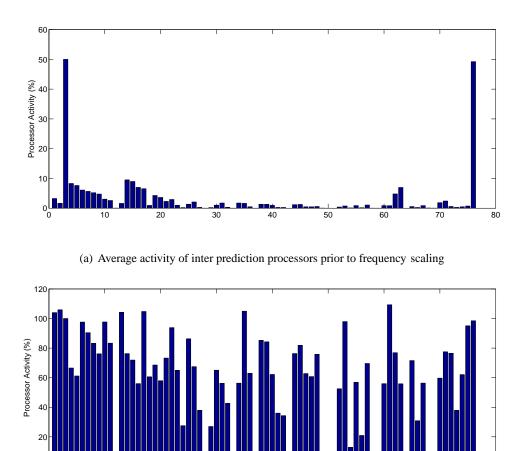

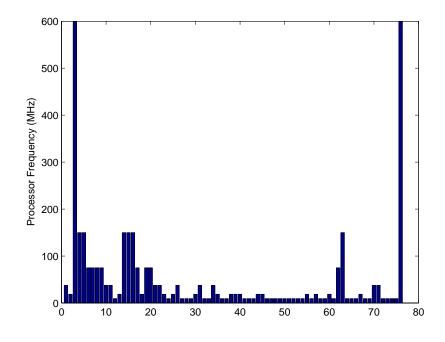

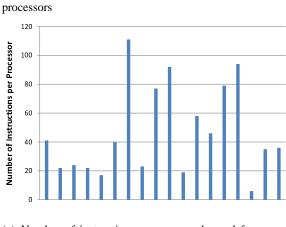

|   |      | 6.3.3          | Processor Utilization                             |   |   |     |   |   |   |   |   | 92       |

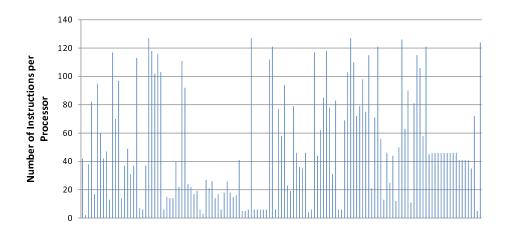

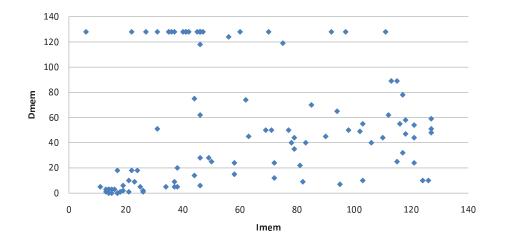

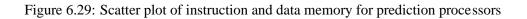

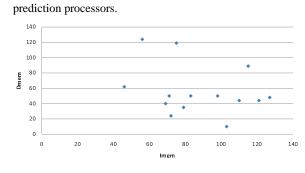

|   |      | 6.3.4          | Processor Memory Usage                            |   |   |     |   |   |   |   |   | 104      |

|   |      | 6.3.5          | Communication                                     | • | • |     | • | • | • | • | • | 104      |

| 7 | Futu | ire Wor        | rk and Conclusion                                 |   |   |     |   |   |   |   |   | 113      |

|   | 7.1  | Archite        | tecture Enhancements for Parallel Programming     |   |   |     |   |   |   |   | • | 113      |

|   |      | 7.1.1          | Multiple I/O Chips                                |   |   | • • |   |   |   |   | • | 113      |

|   |      | 7.1.2          | Multiple Input Processors                         |   |   |     |   |   |   |   | • | 113      |

|   |      | 7.1.3          | Local Shared Memory                               |   |   |     |   |   |   |   |   | 114      |

|   | 7.2  | Tool E         | Enhancements for Parallel Programming             |   |   |     |   |   |   |   |   | 114      |

|   |      | 7.2.1          | Arbitrary Mapping Tool For AsAP2                  |   |   |     |   |   |   |   |   | 114      |

|   |      | 7.2.2          | Analysis of I/O Traffic                           |   |   |     |   |   |   |   |   | 114      |

|   |      |                | -                                                 |   |   |     |   |   |   |   |   |          |

| Bibliogr | raphy                                 | 117 |

|----------|---------------------------------------|-----|

| 7.4      | Conclusion                            | 116 |

| 7.3      | Additional Encoding Functions on AsAP | 115 |

|          | 7.2.3 Enhanced I/O File Operations    | 115 |

# **List of Figures**

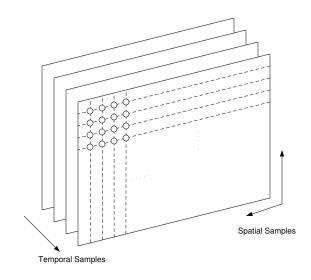

| 2.1  | Temporal and spatial sampling 55                     |

|------|------------------------------------------------------|

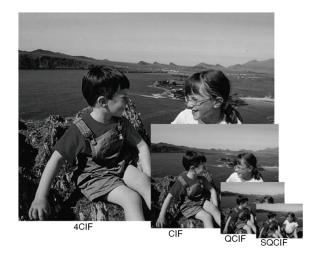

| 2.2  | Sample frame sizes                                   |

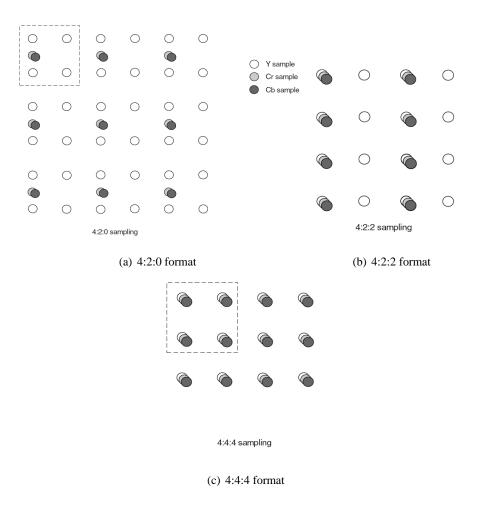

| 2.3  | Various video sampling formats [1]                   |

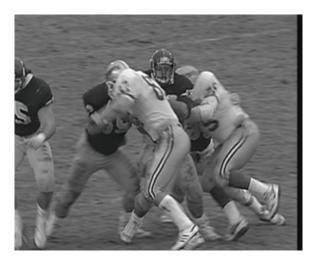

| 2.4  | Y component of YUV                                   |

| 2.5  | U and V Components of YUV picture                    |

| 2.6  | Macro-block partitioning                             |

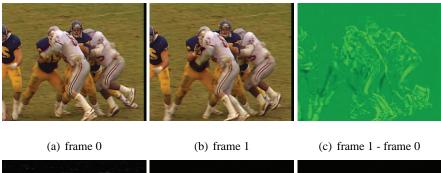

| 2.7  | Difference between two frames                        |

| 2.8  | H.264 encoder path                                   |

| 2.9  | H.264 profiles                                       |

| 2.10 | Intra 16x16 modes                                    |

| 2.11 | Intra 4x4 blocks                                     |

| 2.12 | Intra 4x4 modes                                      |

| 2.13 | Intra chroma modes                                   |

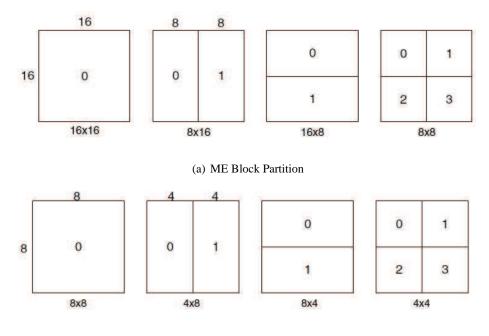

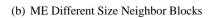

| 2.14 | Macroblock partition for ME                          |

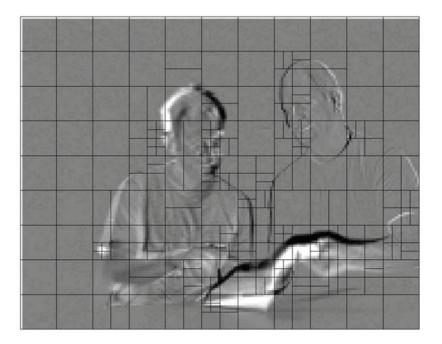

| 2.15 | Sample macroblock partition for ME                   |

| 2.16 | MV prediction from neighboring blocks [1]            |

| 2.17 | Reorder transform blocks                             |

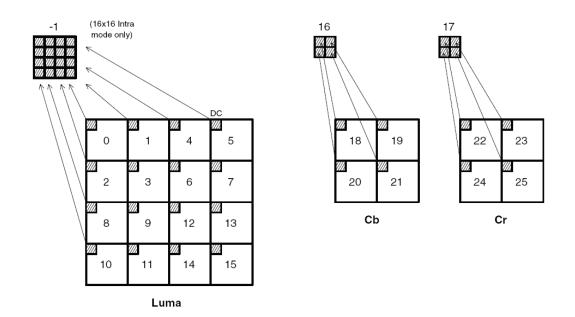

| 2.18 | CAVLC zig zag scan                                   |

| 2.1  |                                                      |

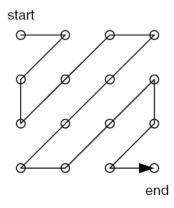

| 3.1  | AsAP array                                           |

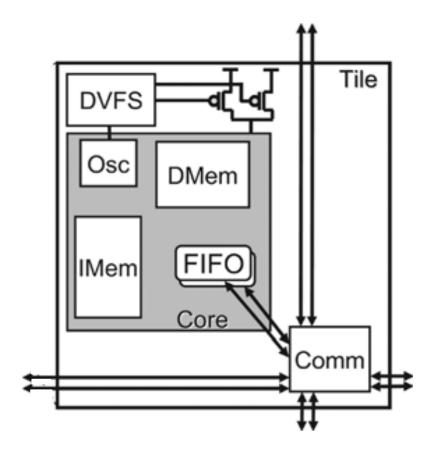

| 3.2  | AsAP processor architecture                          |

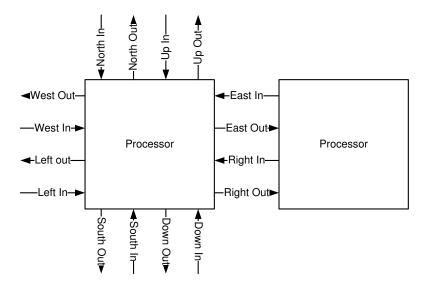

| 3.3  | AsAP nearest neighbor communication                  |

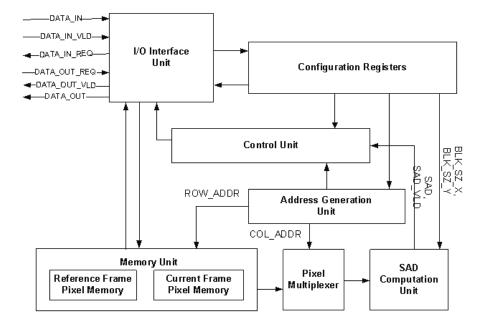

| 3.4  | ME accelerator block diagram                         |

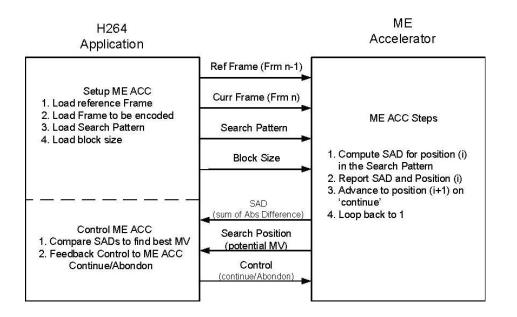

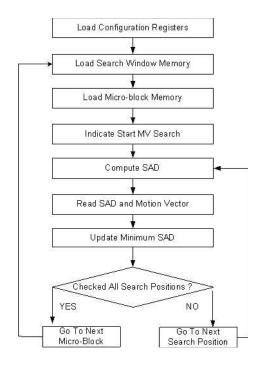

| 3.5  | ME Accelerator control sequence                      |

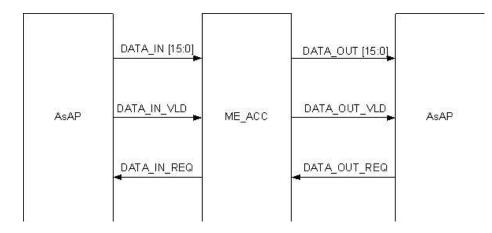

| 3.6  | ME accelerator interface                             |

| 3.7  | ME flow diagram                                      |

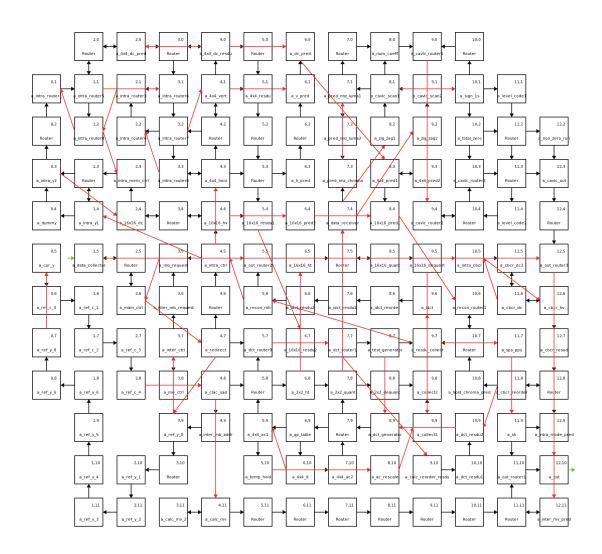

| 4.1  | C model of encoder in asapmap                        |

| 4.2  | Encoder processors in asapmap                        |

| 4.3  | Proposed mapping of processors by asapmap            |

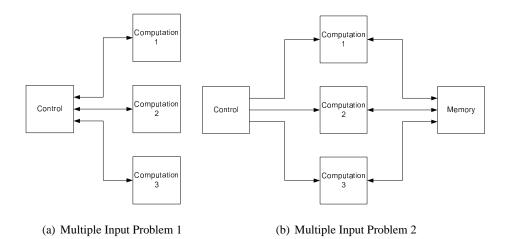

| 4.4  | Problems with more than 3 inputs per processor       |

| 4.5  | Multiple input problem 3       48                    |

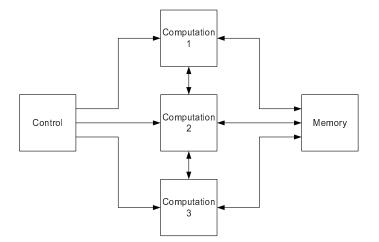

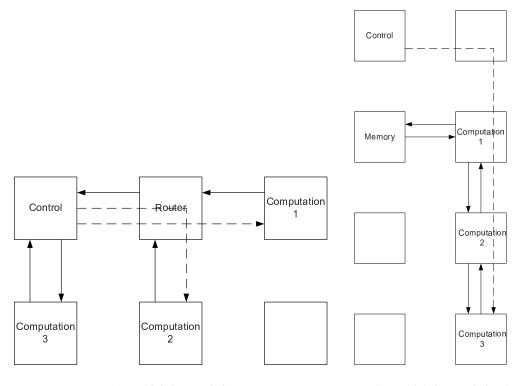

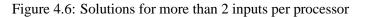

| 4.6  | Solutions for more than 2 inputs per processor       |

| 4.7  | Multiple input solution 3       50                   |

|      |                                                      |

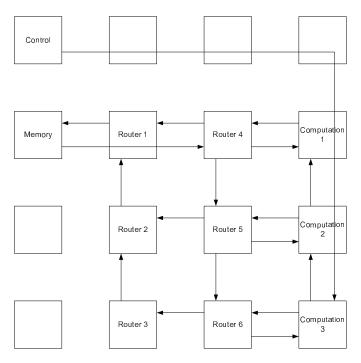

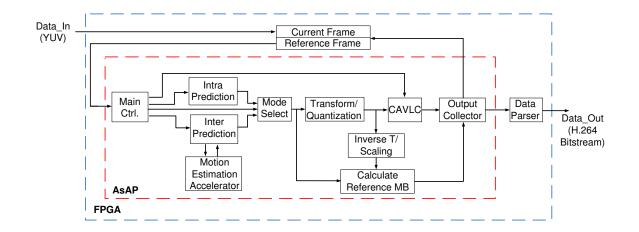

| 5.1  | H.264 encoder path for parallel C/MPI implementation |

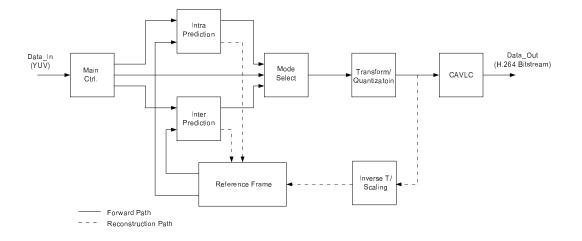

|                                                                                                                                                                                                           | FPGA-AsAP block diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 57                                                                                                                                                         |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.3                                                                                                                                                                                                       | H.264 encoder path - AsAP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 57                                                                                                                                                         |

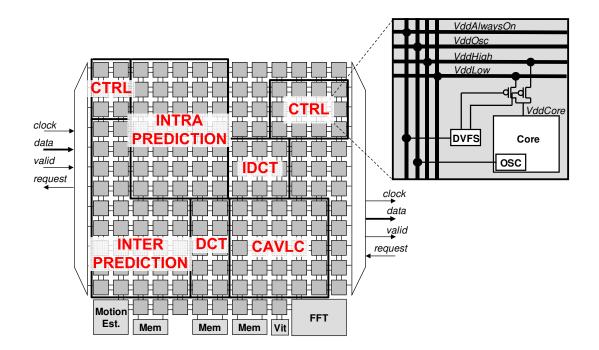

| 5.4                                                                                                                                                                                                       | H.264 blocks on AsAP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 58                                                                                                                                                         |

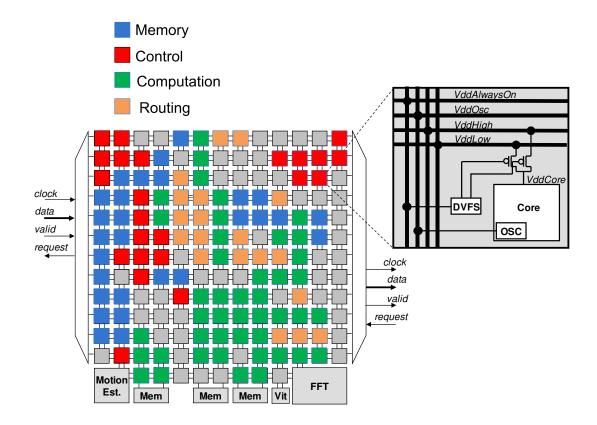

| 5.5                                                                                                                                                                                                       | Partition of processor type on AsAP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 59                                                                                                                                                         |

| 5.6                                                                                                                                                                                                       | Communication links for AsAP implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 60                                                                                                                                                         |

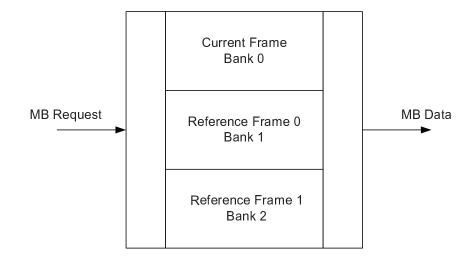

| 5.7                                                                                                                                                                                                       | Current/reference frame on AsAP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 61                                                                                                                                                         |

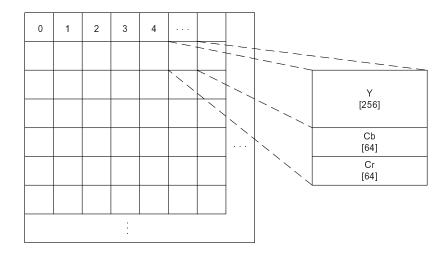

| 5.8                                                                                                                                                                                                       | Macroblock storage in memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 62                                                                                                                                                         |

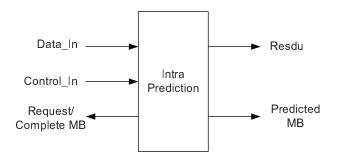

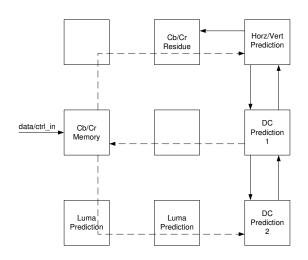

| 5.9                                                                                                                                                                                                       | High level block diagram of intra prediction in AsAP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 64                                                                                                                                                         |

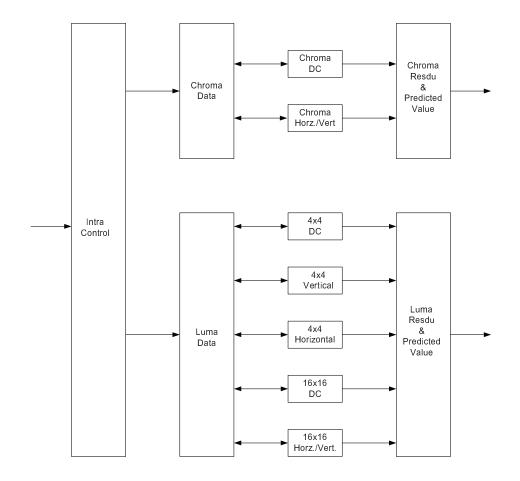

| 5.10                                                                                                                                                                                                      | Intra prediction in AsAP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 65                                                                                                                                                         |

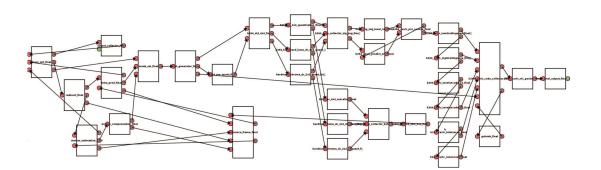

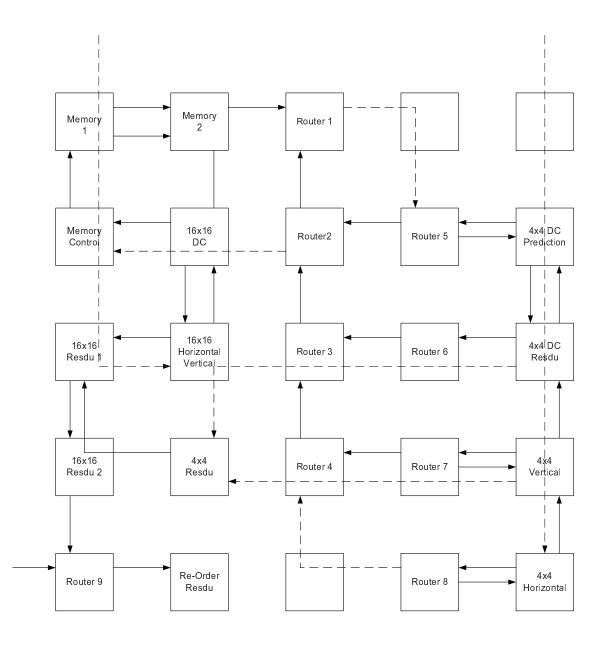

|                                                                                                                                                                                                           | Intra prediction mapping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 67                                                                                                                                                         |

|                                                                                                                                                                                                           | Intra chroma prediction AsAP layout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 68                                                                                                                                                         |

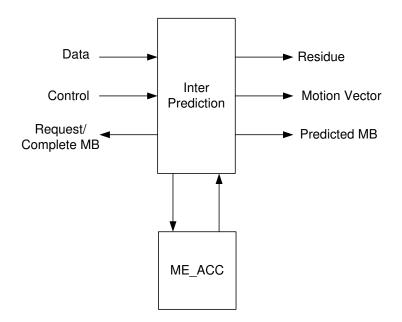

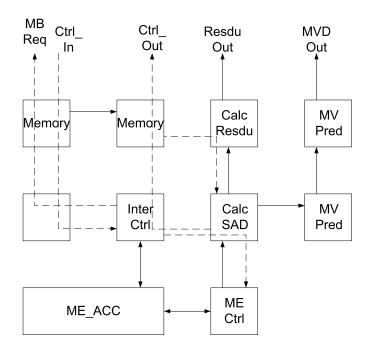

|                                                                                                                                                                                                           | Inter prediction in AsAP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 68                                                                                                                                                         |

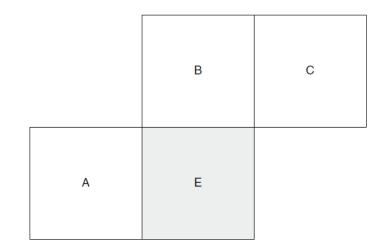

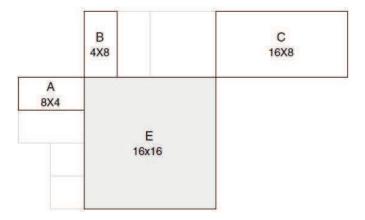

|                                                                                                                                                                                                           | ME_ACC reference macroblock partition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 69                                                                                                                                                         |

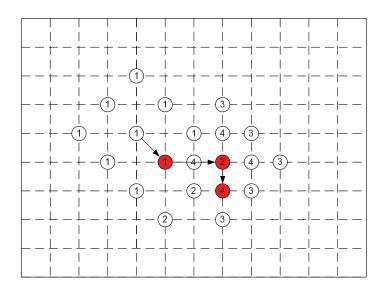

|                                                                                                                                                                                                           | ME diamond search                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 70                                                                                                                                                         |

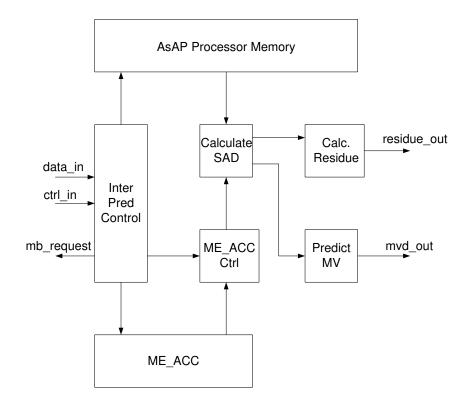

|                                                                                                                                                                                                           | Inter prediction in AsAP block diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 71                                                                                                                                                         |

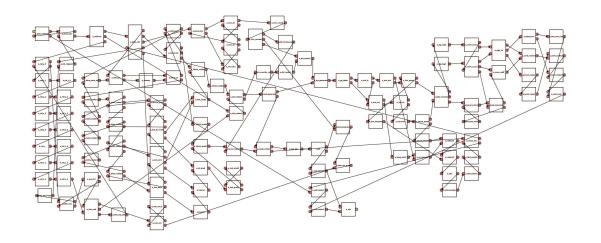

|                                                                                                                                                                                                           | Layout of inter prediction in AsAP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 72                                                                                                                                                         |

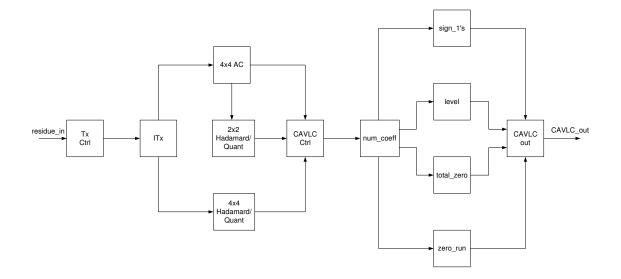

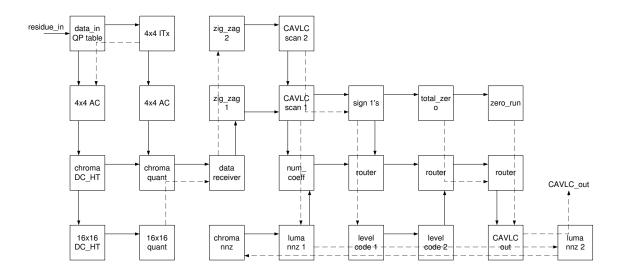

|                                                                                                                                                                                                           | Block diagram of integer transform and CAVLC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 72                                                                                                                                                         |

|                                                                                                                                                                                                           | Layout of integer transform and CAVLC on AsAP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 73                                                                                                                                                         |

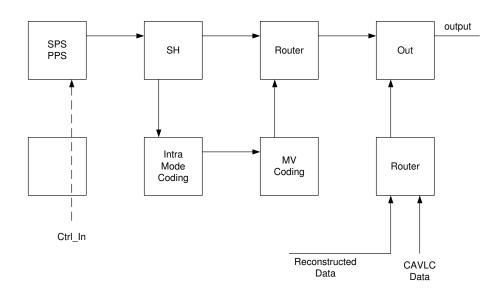

|                                                                                                                                                                                                           | Layout of header module on AsAP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 74                                                                                                                                                         |

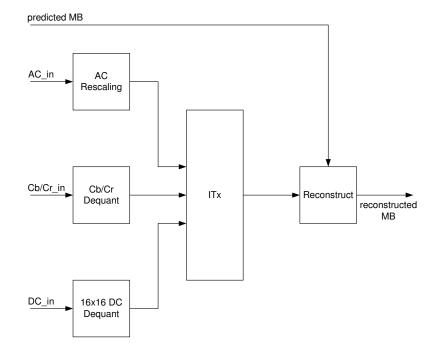

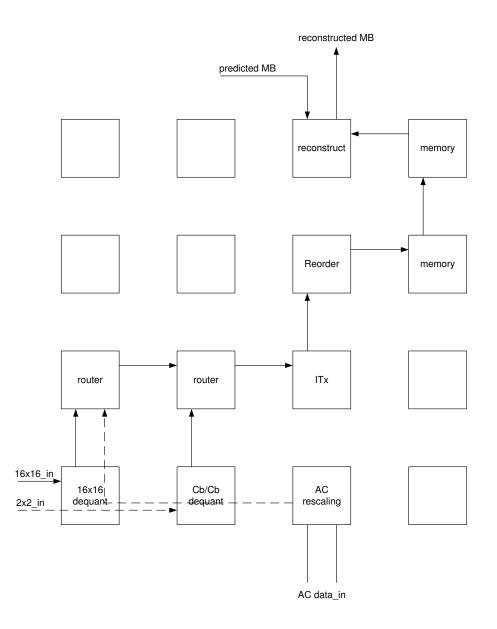

|                                                                                                                                                                                                           | Block diagram of reconstruction module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 74                                                                                                                                                         |

|                                                                                                                                                                                                           | Layout of reconstruction module on AsAP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 75                                                                                                                                                         |

| 0.22                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | , e                                                                                                                                                        |

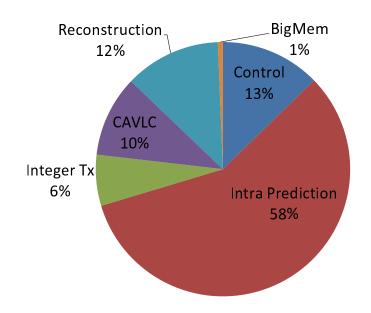

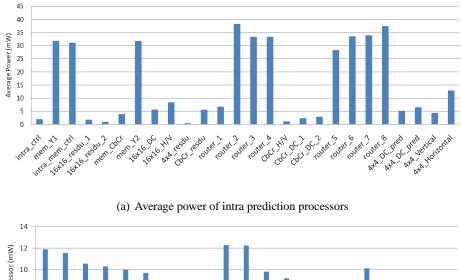

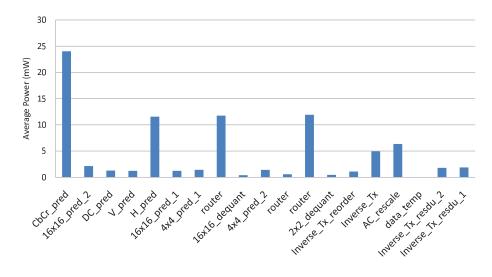

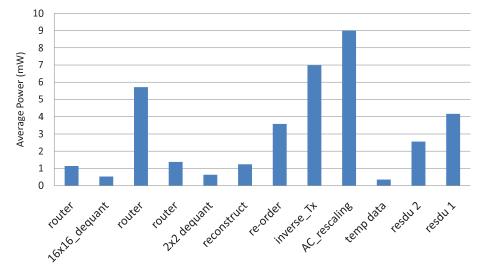

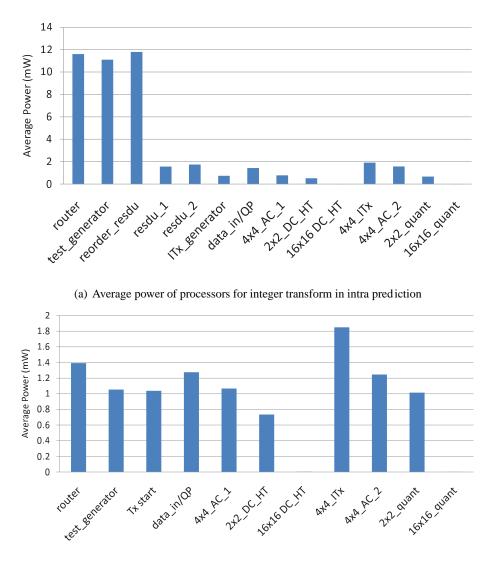

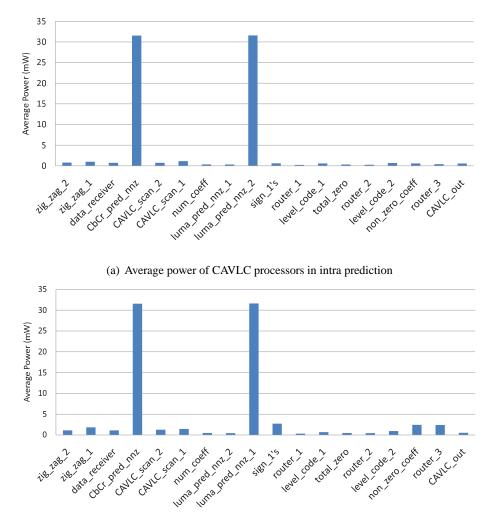

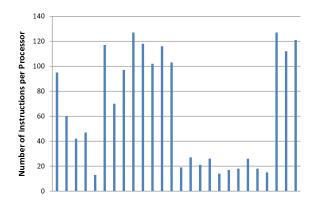

| 6.1                                                                                                                                                                                                       | Power distribution of major blocks in intra prediction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 84                                                                                                                                                         |

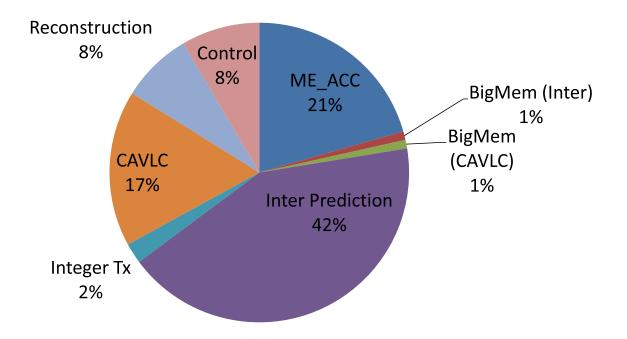

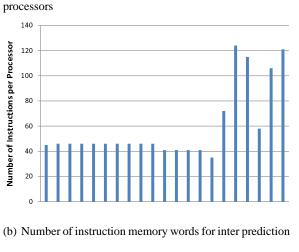

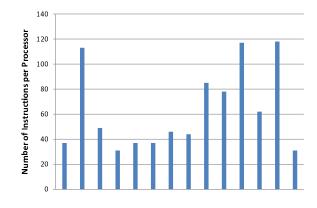

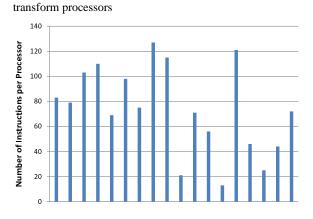

| 6.2                                                                                                                                                                                                       | Power distribution for major blocks in inter prediction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 84                                                                                                                                                         |

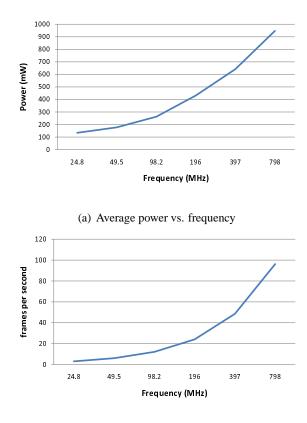

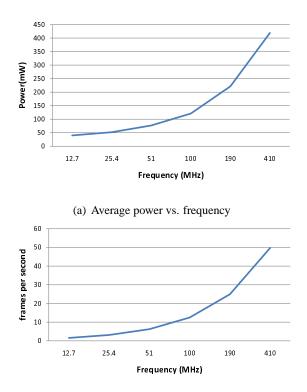

| 6.3                                                                                                                                                                                                       | Average power and number of encoded frames per second vs. frequency at 1.3V on                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                            |

|                                                                                                                                                                                                           | AsAP2 chip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 85                                                                                                                                                         |

|                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                            |

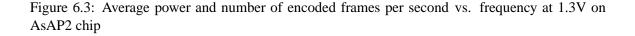

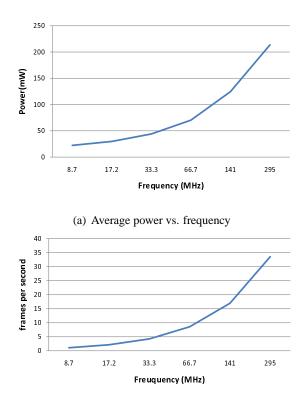

| 6.4                                                                                                                                                                                                       | Average power and number of encoded frames per second vs. frequency at 1.2V on                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                            |

| 6.4                                                                                                                                                                                                       | Average power and number of encoded frames per second vs. frequency at 1.2V on AsAP2 chip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 86                                                                                                                                                         |

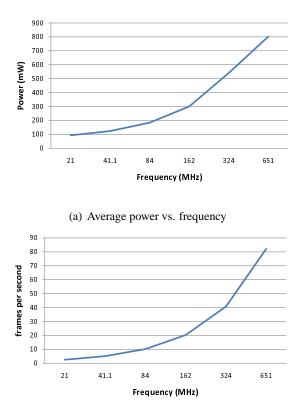

| 6.4<br>6.5                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 86                                                                                                                                                         |

|                                                                                                                                                                                                           | AsAP2 chip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 86<br>87                                                                                                                                                   |

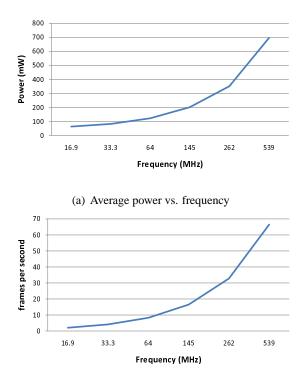

|                                                                                                                                                                                                           | AsAP2 chip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                            |

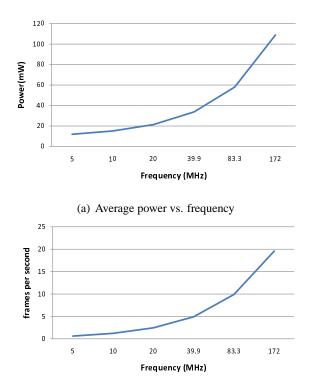

| 6.5                                                                                                                                                                                                       | AsAP2 chip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                            |

| 6.5                                                                                                                                                                                                       | AsAP2 chip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 87                                                                                                                                                         |

| 6.5<br>6.6                                                                                                                                                                                                | AsAP2 chip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 87                                                                                                                                                         |

| 6.5<br>6.6                                                                                                                                                                                                | AsAP2 chip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 87<br>88                                                                                                                                                   |

| 6.5<br>6.6<br>6.7                                                                                                                                                                                         | AsAP2 chipAverage power and number of encoded frames per second vs. frequency at 1.1V onAsAP2 chipAverage power and number of encoded frames per second vs. frequency at 1.0V onAsAP2 chipAverage power and number of encoded frames per second vs. frequency at 0.9V onAsAP2 chipAverage power and number of encoded frames per second vs. frequency at 0.9V onAsAP2 chip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 87<br>88                                                                                                                                                   |

| 6.5<br>6.6<br>6.7                                                                                                                                                                                         | AsAP2 chipAverage power and number of encoded frames per second vs. frequency at 1.1V onAsAP2 chipAverage power and number of encoded frames per second vs. frequency at 1.0V onAsAP2 chipAverage power and number of encoded frames per second vs. frequency at 0.0V onAsAP2 chipAverage power and number of encoded frames per second vs. frequency at 0.9V onAsAP2 chipAverage power and number of encoded frames per second vs. frequency at 0.9V onAsAP2 chipAverage power and number of encoded frames per second vs. frequency at 0.8V on                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 87<br>88<br>89                                                                                                                                             |

| <ul> <li>6.5</li> <li>6.6</li> <li>6.7</li> <li>6.8</li> <li>6.9</li> </ul>                                                                                                                               | AsAP2 chip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 87<br>88<br>89<br>90                                                                                                                                       |