## Implementation of Context-Based Adaptive Binary Arithmetic Coding on KiloCore Processor Arrays

By

#### SHARMILA SRIRANGA KULKARNI

#### THESIS

Submitted in partial satisfaction of the requirements for the degree of

MASTER OF SCIENCE

in

Electrical and Computer Engineering

in the

#### OFFICE OF GRADUATE STUDIES

of the

#### UNIVERSITY OF CALIFORNIA

DAVIS

Approved:

Chair, Dr. Bevan M. Baas

Member, Dr. Venkatesh Akella

Member, Dr. Soheil Ghiasi

Committee in charge 2021

© Copyright by Sharmila Sriranga Kulkarni 2021 All Rights Reserved

## Abstract

H.264/AVC is a popular video coding standard used in the fields of communication, video streaming and broadcasting. The H.264/AVC standard as specified in ITU-T — ISO/IEC has two methods of entropy coding, namely Context-based Adaptive Variable Length Coding (CAVLC) and Context-based Adaptive Binary Arithmetic Coding (CABAC). CABAC utilizes probability estimation to achieve a bit-rate reduction of 19% compared to CAVLC.

In order to deal with the higher level of computational complexity of the CABAC entropy coding over the CAVLC coding, the CABAC algorithm is sometimes implemented in hardware to achieve realtime high resolution video coding. The CABAC algorithm can be broken into smaller tasks that can be performed independently. This makes the many-core processor array an appropriate option for the hardware implementation of the CABAC encoding algorithm. The independent tasks within the algorithm can be assigned to individual cores of the array. The KiloCore II, which this thesis uses for its hardware platform, contains hundreds of programmable processors and multiple 64kB shared memories per chip. Lanes of processors are constructed to perform the functions of the blocks within the CABAC.

The aim of this thesis is to compare the throughput results with existing hardware and software implementations of CABAC and to show that the throughput, power and energy in the case of the KiloCore II is competitive. The CABAC algorithm was mapped on the KiloCore II array using the Project manager and Simulator platform. The total area occupied by the algorithm was  $3.52 \text{ mm}^2$  in 32 nm technology with 64 cores and 177 routing links. The implementation achieved a throughput of 37 million bins per second at 1.1 V operating voltage and an energy of  $34.37 \mu \text{J}$  per individual bin at 0.8 V operating voltage.

This implementation of the CABAC has an improvement of 57 times in throughput, when compared to the software implementation, that is, the JM software reference run on the Intel Xeon Processor E5-2680 v2. Despite being a fully-software implementation, the presented KiloCore design achieves a throughput within a factor of five when compared to hardware CABAC implementations scaled to the same 32 nm fabrication technology.

## Acknowledgments

The body of work that is described in this thesis has been a major part of my masters and would not be possible without the support and help of so many people. Firstly, I would like to thank Professor Bevan Baas for inspiring me to challenge myself and take up this project. Professor Baas was always available with his guidance and his time, which is greatly appreciated.

I would like to thank Professor Venkatesh Akella and Professor Soheil Ghiasi for serving on my thesis committee and for reviewing my work.

I would like to extend my gratitude towards Renjie Chen for giving me a detailed introduction into the working of CABAC. I am grateful for the work done by Brent Bohenstiehl on the Project Manager and the Compiler, tools which I utilized to complete my research. I would like to thank Mark Hildebrand and Satyabrata Sarangi for their work on the Mapper software and the DeepScaleTool respectively, which were important tools that made my work easier. I am thankful for the help and assistance I received from my fellow lab members Yushan Wu and Filipe Borges. I am grateful for Shifu Wu, Timothy Andreas for their advice, support and informative tutorials.

I am eternally grateful for all the support I received from my family. Their encouragement and belief in me helped me through the course of my research.

# Contents

| A             | bstra                                  | let                                                                                                                                                                                                                                                                                                                  | ii                                                                                                                     |

|---------------|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| A             | cknov                                  | wledgments                                                                                                                                                                                                                                                                                                           | iii                                                                                                                    |

| $\mathbf{Li}$ | st of                                  | Figures                                                                                                                                                                                                                                                                                                              | vi                                                                                                                     |

| $\mathbf{Li}$ | st of                                  | Tables                                                                                                                                                                                                                                                                                                               | iii                                                                                                                    |

| 1             | <b>Intr</b><br>1.1<br>1.2              | oduction<br>Motivation                                                                                                                                                                                                                                                                                               | <b>1</b><br>1<br>2                                                                                                     |

| 2             | <b>Ove</b><br>2.1<br>2.2               | erview of H.264/Advanced VideoCoding (AVC) Standard         Overview of H.264/AVC         2.1.1       Macroblocks and Slices         2.1.2       Encoding process of H.264         Context-based Adaptive Binary Arithmetic Coding (CABAC)         2.2.1       Overview of CABAC         2.2.2       Syntax elements | <b>3</b><br>3<br>4<br>6<br>8<br>9<br>12                                                                                |

| 3             | <b>The</b><br>3.1<br>3.2<br>3.3<br>3.4 | e KiloCore Many-Core Processor Array Architecture         Processors         Memory         Communication between processors                                                                                                                                                                                         | 12<br>16<br>17<br>17<br>18                                                                                             |

| 4             | Met<br>4.1<br>4.2                      | Overview                                                                                                                                                                                                                                                                                                             | <ul> <li>20</li> <li>20</li> <li>22</li> <li>25</li> <li>27</li> <li>27</li> <li>29</li> <li>30</li> <li>30</li> </ul> |

|               | 4.3                                    | 4.3.1 Context index increment computation cores                                                                                                                                                                                                                                                                      | 35<br>38<br>47                                                                                                         |

|          | 4.4                    | Binary Arithmetic Encoder                                  | 47        |

|----------|------------------------|------------------------------------------------------------|-----------|

| <b>5</b> | $\mathbf{J}\mathbf{M}$ | software and functional verification                       | <b>55</b> |

|          | 5.1                    | JM software                                                | 55        |

|          | 5.2                    | Binarization verification                                  | 56        |

|          |                        | 5.2.1 Debugging the binarizer                              | 57        |

|          | 5.3                    | Context Modeler verification                               |           |

|          | 5.4                    | Binary Arithmetic encoder verification                     |           |

|          |                        | 5.4.1 Debugging the Context modeler and Arithmetic Encoder | 59        |

| 6        | $\mathbf{Exp}$         | erimental Results and Analysis                             | 61        |

|          | 6.1                    | Analysis of core usage                                     | 61        |

|          |                        | 6.1.1 Mapping to the KiloCore II                           | 64        |

|          | 6.2                    | Throughput and energy results                              | 66        |

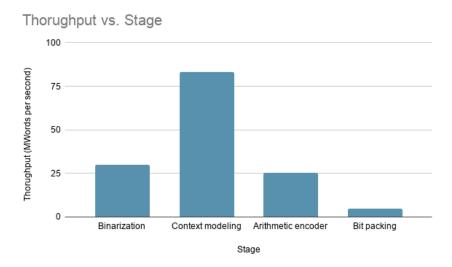

|          |                        | 6.2.1 Throughput through the stages                        | 66        |

|          |                        | 6.2.2 Scaling with Voltage results                         | 68        |

|          |                        | 6.2.3 Energy results                                       | 70        |

|          | 6.3                    | Comparison with other implementations of CABAC             | 70        |

| 7        | The                    | sis summary and Future work                                | <b>74</b> |

|          | 7.1                    | Thesis summary                                             | 74        |

|          | 7.2                    | Future work                                                | 74        |

|          |                        | 7.2.1 Improving Throughput and energy                      | 75        |

| Bi       | bliog                  | raphy                                                      | 77        |

# List of Figures

| $2.1 \\ 2.2$ | Progressive and interlaced frames and fields [1]                                                        | 4        |

|--------------|---------------------------------------------------------------------------------------------------------|----------|

| 2.2<br>2.3   | 4:2:0 Sampling of YCbCr color space [2]                                                                 | $5\\5$   |

| 2.3<br>2.4   | H.264 coding structure for a macroblock [1]                                                             | 6        |

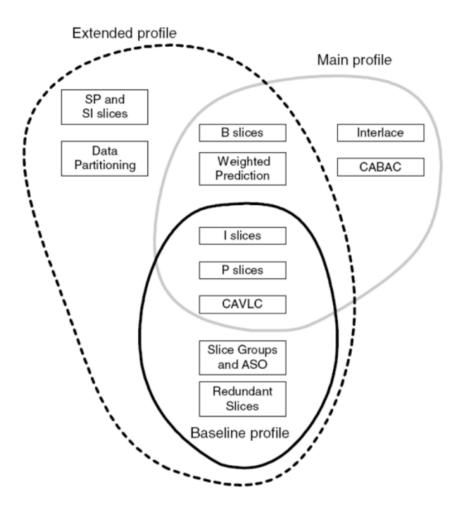

| 2.4<br>2.5   | H.264/AVC profiles $[2]$                                                                                | 7        |

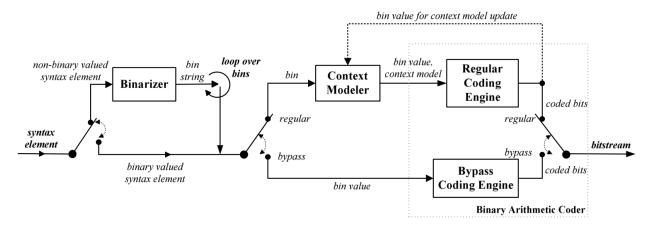

| 2.6          | CABAC encoding engine [3]                                                                               | 9        |

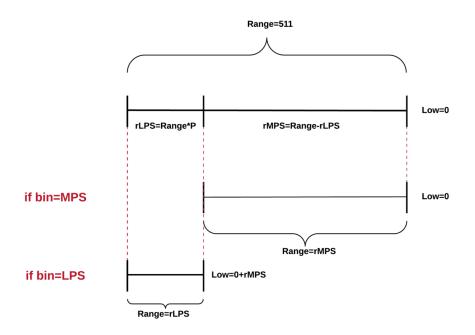

| 2.0<br>2.7   | Updating the Range and Low variables in BAE                                                             | 11       |

| 2.8          | Updating the Range and Low variables in BAE                                                             | 12       |

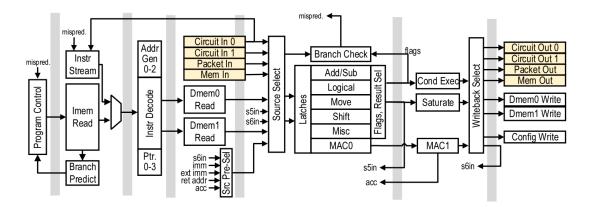

| 3.1          | KiloCore pipeline [4]                                                                                   | 17       |

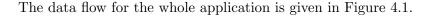

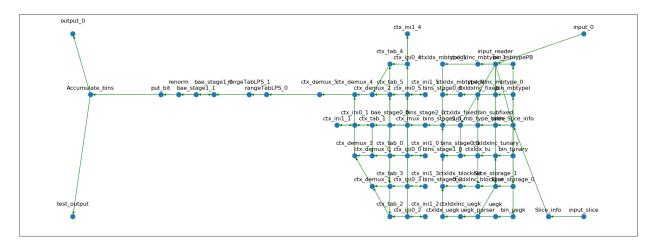

| 4.1          | CABAC data flow                                                                                         | 20       |

| 4.2          | I was seen to be a set of the set                                                                       | 21       |

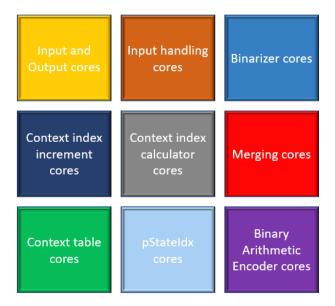

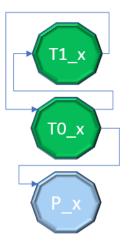

| 4.3          | Colors of various stages of cores                                                                       | 22       |

| 4.4          | Complete input and output connections of the core $bin_distributor(I_2)$ . I_0: in-                     |          |

|              |                                                                                                         | 23       |

| 4.5          | Complete input and output connections of the core <i>input_reader</i> (I_0) and <i>slice_mb_storage</i> |          |

|              | (I_3). I_2: bin_distributor, C_0: ctxIdxInc_mbtype, C_1: ctxIdxInc_fixed, C_2: ctxIdx-                  |          |

|              | $Inc\_blockcat, C\_3: ctxIdxInc\_tunary, C\_4: uegk\_parser $                                           | 24       |

| 4.6          | 0                                                                                                       | 33       |

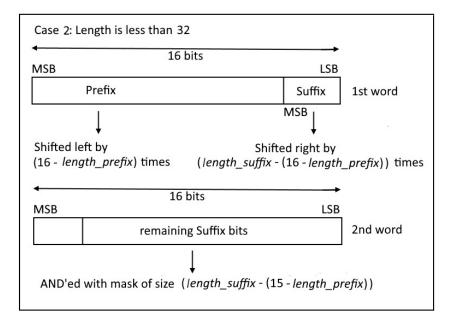

| 4.7          | Prefix and Suffix words in 16-bit register: Case 2                                                      | 33       |

| 4.8          | Prefix and Suffix words in 16-bit register: Case 3                                                      | 34       |

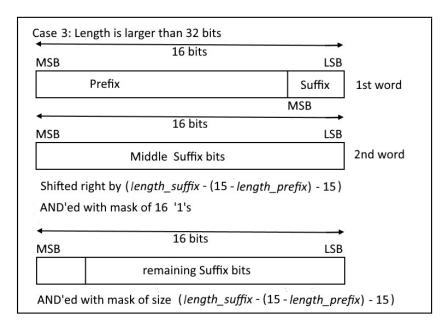

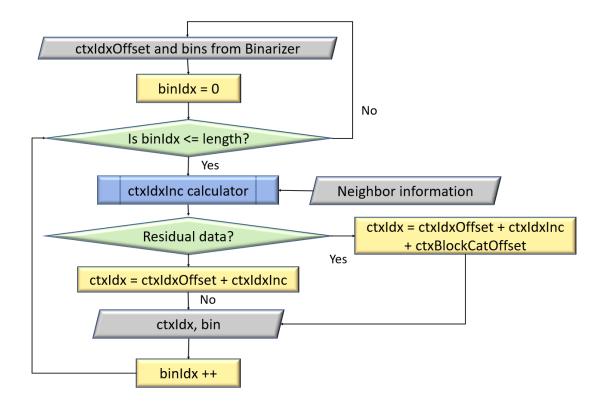

| 4.9          | Flowchart of the Context modeler block                                                                  | 36       |

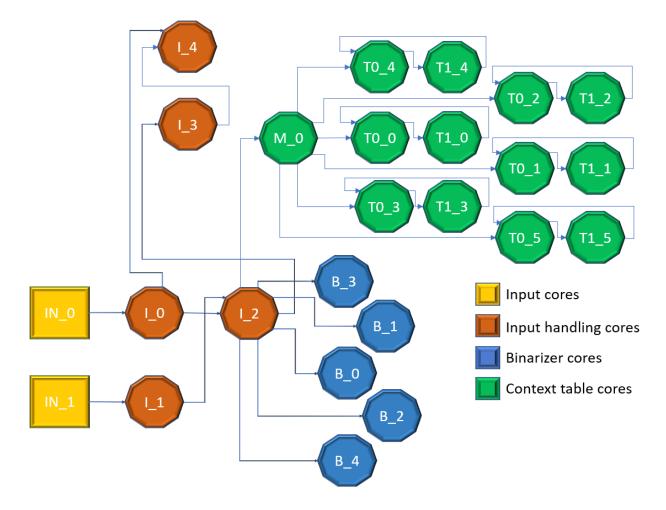

| 4.10         | Connections for the Context modeler block. B_0 to B_6 are the binarizer block cores.                    |          |

|              | $C_0$ to $C_5$ are the context index increment cores. $C_6$ to $C_{10}$ are the context index           |          |

| 4 1 1        | 0                                                                                                       | 37       |

|              | 8                                                                                                       | 38       |

|              | 8                                                                                                       | 45       |

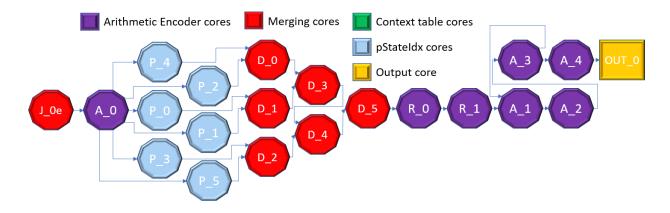

|              |                                                                                                         | 48       |

| 4.14         | Connections for the Binary arithmetic encoder block. J_0e is the last <i>bin_join</i> core.             |          |

|              | A_0: bae_stage0_0, P_X: pStateIdx cores, D_X: Demux cores, R_X: rangeTableLPS                           | 40       |

| 4.15         |                                                                                                         | 49<br>50 |

| 4.15         | Connection between the Context table cores and the pStateIdx cores                                      | 50       |

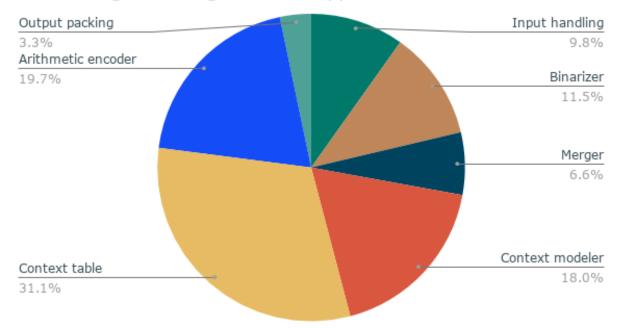

| 6.1          | 0                                                                                                       | 62       |

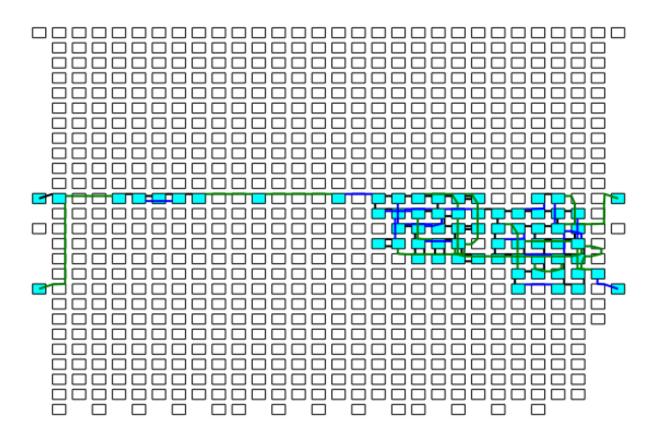

| 6.2          | 11 0                                                                                                    | 64       |

| 6.3          | 1                                                                                                       | 65       |

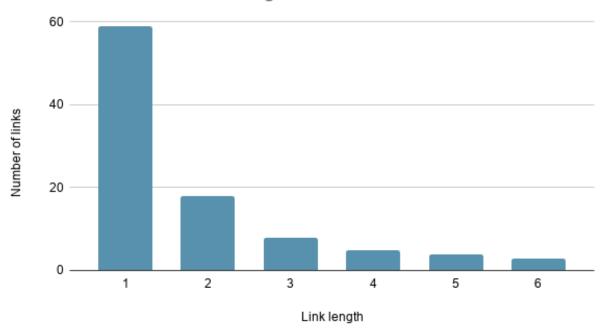

| 6.4          | Chart showing link length data                                                                          | 66       |

| 6.5 | Throughput of the stages                                     | 68 |

|-----|--------------------------------------------------------------|----|

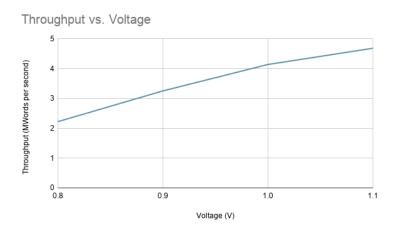

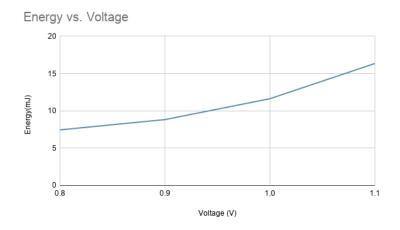

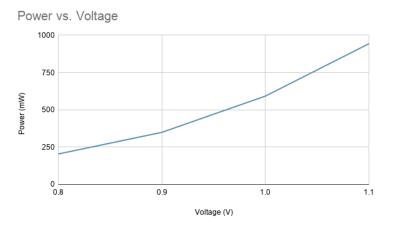

| 6.6 | Throughput variation with Voltage                            | 69 |

| 6.7 | Energy variation with Voltage                                | 69 |

| 6.8 | Power variation with Voltage                                 | 69 |

| 7.1 | Neighbor information to be stored for ctxIdx calculation [6] | 75 |

# List of Tables

| 2.1  | Syntax element categories for CABAC                                                                   | 13 |

|------|-------------------------------------------------------------------------------------------------------|----|

| 4.1  | Input varaibles from JM software                                                                      | 22 |

| 4.2  | Values of ctxIdxOffset for each syntax element type                                                   | 26 |

| 4.3  | Example of fixed length coding when $cmax = 7$ [6] $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 29 |

| 4.4  | cmax values for truncated unary coding                                                                | 30 |

| 4.5  | Parameters for UEGk coding                                                                            | 31 |

| 4.6  | Macroblock partition categories                                                                       | 40 |

| 4.7  | Sub-macroblock sub-partition categories                                                               | 40 |

| 4.8  | Indices representing partition type                                                                   | 41 |

| 4.9  | Indices for when partitions are $8x8$                                                                 | 42 |

| 4.10 | Indices for when partitions are $4x4$                                                                 | 42 |

| 4.11 | Categories of transform block                                                                         | 46 |

| 4.12 | ctxIdxBlockCatOffset based on the syntax element and ctxBlockCat $\ldots \ldots \ldots$               | 47 |

| 4.13 | Range of ctxIdx handled by each pState core                                                           | 51 |

| 5.1  | JM generated file information                                                                         | 56 |

| 5.2  | Ranges of syntax elements                                                                             | 57 |

| 5.3  | File test_output variables                                                                            | 59 |

| 6.1  | Area usage per task                                                                                   | 63 |

| 6.2  | Mapper details about links                                                                            | 65 |

| 6.3  | Stage-wise throughput                                                                                 | 67 |

| 6.4  | Effects of voltage                                                                                    | 70 |

| 6.5  | Energy per bin measurements                                                                           | 70 |

| 6.6  | CABAC throughput measurements                                                                         | 72 |

| 6.7  | CABAC scaled measurements                                                                             | 73 |

# Chapter 1

# Introduction

## 1.1 Motivation

With the ever-increasing demand and consumption of streaming video content across the globe, be it Netflix, Youtube, Tiktok or Zoom meetings, the underlying algorithm for video transmission has to be well-tuned to deal with variable internet speeds and not allow video buffering. As a result, there is a pressing need to come up with good data compression techniques and improve upon existing ones. The H.264 Advanced Video Coding (AVC) standard provides very good data compression, making it a popular algorithm for video or data coding and transmission.

The two methods of entropy coding available in the H.264/AVC standard are Context-based Adaptive Variable Length Coding (CAVLC) and Context-based Adaptive Binary Arithmetic Coding (CABAC). CABAC particularly, is able to reduce the data redundancy based on its statistical property and is able to achieve a significantly higher compression ratio especially for video with high resolution. The CABAC algorithm can be broken into many small tasks that can be performed independently. With the CABAC hardware implementation, it is possible to reduce the storage and resource cost by running multiple arithmetic encoding engines at the low level (coding block) and enabling the pipeline within the arithmetic coding engine. This makes the many-core processor array an appropriate option for the hardware implementation of the CABAC encoding algorithm.

The Kilcore 2 processor array contains 1000 processors that can be independently programmed. The instruction memory in each core is 128x40b. This allows a small task from the CABAC to fit on each processor. Communication between cores (processors) on the chip is through a highly reliable Circuit switched link. Each processor has two input buffers for the processing of this input data. Each core also has 8 output ports. This allows us to fan out the information being processed by the input handling cores, to perform the tasks in parallel. The goal of this research is provide the Implementation of CABAC on KiloCore II and a comparative analysis of the performance of the KiloCore II implementation of the CABAC with other existing hardware implementations. Due to serial processing nature of the Binary Arithmetic Encoder, parallelism at the slice level in the CABAC is challenging [7]. Task parallelism is employed for the probability state variables updating in this implementation.

#### **1.2** Thesis Organization

The thesis chapters are organized as follows.

Chapter 2 gives a background on the H.264 standard. In particular, information on the CABAC algorithm is provided here in detail, including explanation of the CABAC encoding engine, the CABAC implementation along with all the syntax elements used in the CABAC coding process.

Chapter 3 explains the working of the Multi-core processor array, KiloCore Platform, with details on the Processors, Memory and Inter-Processor Communication.

Chapter 4 details the methodology of the CABAC implementation with the following subsections: one on Input Data handling, input output connections of the cores, a subsection on the Binarizer implementation with its constituent cores, syntax elements and the coding methods and algorithms used, a subsection with a detailed explanation on the working of the Context Modeler with its constituent cores and Content Index calculation, and finally a subsection on the Binary Arithmetic Encoder with its cores and algorithms.

Chapter 5 gives the Functional verification. Firstly it talks about the H.264 JM reference software which is used as the reference for functional verification. The CABAC related configuration of JM encoder and the testing methodology are explained. Then the Binarizer verification, Context Modeler verification is listed.

Chapter 6 has the Experimental results and analysis. The Results of throughput and energy are presented. The analysis is done by taking comparisons from previous works and implementations of CABAC on different hardware platforms.

# Chapter 2

# Overview of H.264/Advanced VideoCoding (AVC) Standard

## 2.1 Overview of H.264/AVC

The H.264/AVC standard as described by the Telecommunication Standardization Sector of International Telecommunication Union (ITU-T) details the encoding and decoding of video. As demand for video streaming has gone up, so has the resolution, thus greatly increasing file sizes to be stored and transmitted over the network. The raw video files are compressed for storage and transmission in accordance with the H.264/AVC standard. The Motion Pictures Experts Group (MPEG) and the Video Coding Experts Group (VCEG) developed the standard. The popularity for the standard is due to the good graphic quality despite having high compression rates. Compared with existing standards, H.264/AVC provides improvements in rate-distortion efficiency [1].

H.264/AVC standard has found significance in the areas of broadcast, satellite, storage (optical or magnetic storage devices), LAN, modem, wireless or mobile networks, streaming services, Multimedia messaging services and many more.

The standard elaborates on Video Coding Layer (VCL), which is used to represent the video content, and on Network Abstraction Layer (NAL), which is responsible for generating header information, either for transmitting the video coded data over the network or for storage. The Video Coding Layer is the portion of the standard that will be discussed here, given that the Entropy coding methods make up a part of the VCL.

The flexibility that is availed by the standard is due to improvements in motion compensation, motion vector accuracy, reference picture increase, better prediction methods, improvements in transform, data partitioning and introduction of entropy coding.

Some of the salient features of the H.264 algorithm are explained in this section. Macroblocks and Slices, explained in Section 2.1.1, make up the building blocks of the representation of images in the video being encoded. The encoding process is detailed in Section 2.1.2.

#### 2.1.1 Macroblocks and Slices

In the VCL, coded pictures make up a coded video sequence. Each coded picture is represented in block-shaped units of its constituent luma and chroma samples. These block units are called Macroblocks.

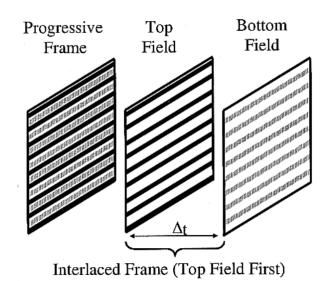

Figure 2.1: Progressive and interlaced frames and fields [1]

A coded picture can either be a frame or a field. A frame consists of a top and bottom field which are interleaved in the frame. The top field contains the even-numbered rows and the bottom field contains the odd-numbered rows. When the two fields are captured at different points of time, the frame is called an interlaced frame otherwise called a progressive frame [1]. Figure 2.1 shows the interlaced and progressive frames.

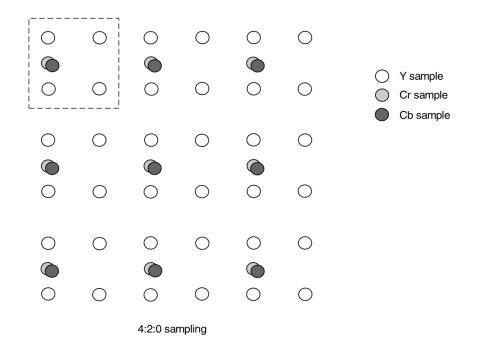

The brightness and color information is represented using the YCbCr color space. The chroma information (CbCr) has one fourth of the sampling resolution compared with the luma (Y) information. This is called 4:2:0 sampling, with each sample being 8 bits, is shown in Figure 2.2.

Each picture is divided into Macroblocks which each contain 16x16 samples of the luma component and 8x8 smaples of the two chroma components.

Figure 2.2: 4:2:0 Sampling of YCbCr color space [2]

A sequence of macroblocks in a raster scan order make up a slice. There are three types of slices used in the Main profile of H.264/AVC. They are the I slice, the P slice and the B slice.

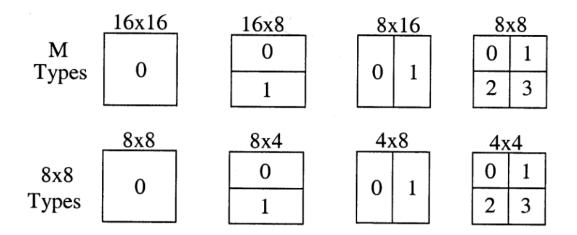

Figure 2.3: Macroblock and submacroblock partitions [1]

The I slice is the one within which all the macroblocks are coded using intra prediction. The P slice uses inter prediction with only one motion-compensated prediction signal for some macroblocks, along with intra-prediction. Finally the B slice, which along with the P slice coding prediction methods, can also use two motion-compensated prediction signals per prediction block.

**Macroblock partitioning** Each macroblock contains 256 pixels (16x16 square). These macroblocks can be further partitioned into submacroblocks, which in turn can also be partitioned again. The 16x16 macroblock can be partitioned into 16x8, 8x16 or 8x8 partitions. The 8x8 submacroblock can be partitioned into 8x4, 4x8 and 4x4 sub-partitions. These partitions are shown in Figure 2.3.

Figure 2.4: H.264 coding structure for a macroblock [1]

#### 2.1.2 Encoding process of H.264

The encoding consists of four stages. The first stage is Prediction, of which there are two types. Inter and Intra prediction. In intra prediction, the signal is predicted only from previously coded samples of the same slice. In inter prediction, the signal is predicted using coded samples of both before and after the current sample in the sequence. The residual data, which is the difference between the prediction and the original picture, is sent to the next stage which is the Transform stage. Here coefficients are produced by using an interger transform such as Discrete Cosine Transform (DCT). The produced coefficients are quantized in the third stage. Finally the quantized coefficients are converted into a bit stream using the entropy encoder. The coding procedure is shown in Figure 2.3.

There are three profiles for the H.264/AVC standard, based on requirements of the applications. They are Baseline, Main and Extended profile.

Figure 2.5: H.264/AVC profiles [2]

The profiles and their salient features are shown in Figure 2.4. In this body of work, the main profile is used as it includes the CABAC encoding engine.

There is a fully-parallel H.264/AVC baseline encoder on a 167-core asynchronous array of simple processors(AsAP) computation platform [8]. However, this implementation uses the other entropy encoding method, namely the Context-based Adaptive Variable Length Coding (CAVLC) [9]. Another paper [10] focuses on the parallelization of the H.264/AVC baseline residual encoder and CAVLC.

## 2.2 Context-based Adaptive Binary Arithmetic Coding (CABAC)

Entropy coding is an inherently lossless compression scheme which, based on its statistical property, reduces the redundancy of the input data. Some of the most commonly used entropy coding techniques are Run Length Coding (RLC), Huffman coding and arithmetic coding. The H.264 standard uses CAVLC or Context-Adaptive Variable-Length Coding for baseline profile, and CABAC or Context-based Adaptive Binary Arithmetic Coding is applied for main profile, extended profile and also high profile.

The CAVLC, in addition to being adopted for encoding the zig-zag order transformed residual coefficients, is also used in the prediction modes of intra prediction and the motion vectors of inter prediction. Huffman coding is applied in CAVLC for coding transform coefficients and Exponential Golomb coding is used for encoding the prediction modes and motion vectors.

CABAC utilizes a special scheme of binary arithmetic coding for encoding the semantics of the syntax elements (SE) from previous H.264 coding procedures. These include the type of macroblock, reference index and motion vector difference in inter prediction, prediction modes in intra prediction, parameters for quantization, residual data parameters and coefficients. Both binary and non-binary syntax elements can be encoded by CABAC, while the non-binary syntax element will get binarized before being coded in arithmetic coding. During binary arithmetic coding process, a probability model, or the context model as it is known, is selected adaptively based on the local coding context, which includes the previous coded information in current coding macroblock, as also the neighboring macroblocks information.

This adaptive selection of context model in CABAC allows for a more accurate probability modeling than the conventional arithmetic coding scheme, as a result of which CABAC achieves high compression performance. In addition, CABAC is a multiplication-free coding system, where, without the use of multiplication, the interval division and probability updating process in arithmetic coding is implemented by table a look-up algorithm which is based on quantized probability states and quantized interval range. Hence, CABAC achieves accelerated computation when compared to conventional multiplication-based arithmetic coding.

As can be seen by the coding performance evaluation in [11], CABAC achieves an average bit rate reduction of 15 percent to 19 percent over CAVLC when tested video sequences with different formats. With higher definition ideo sequence, the reduction in bit rate over CAVLC is more significant. Hence, considering the current increasing demand for high resolution video, CABAC is a promising entropy coding option.

The next subsection explains in detain about the CABAC algorithm and the stages involved in it. The processing element, namely the Syntax element is also further explained in the following subsection.

#### 2.2.1 Overview of CABAC

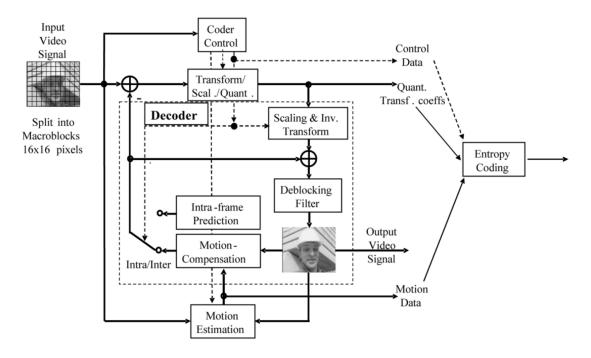

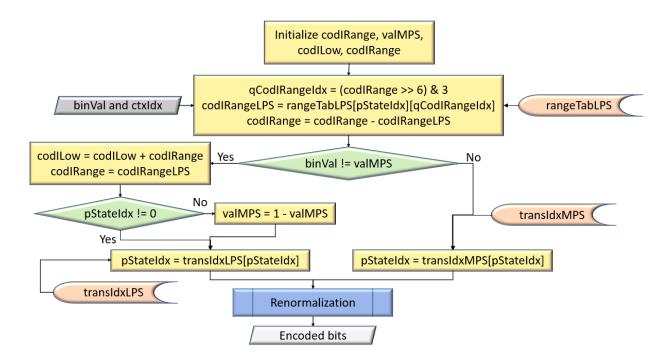

The CABAC coding has three elementary procedures: binarization, context modeling (CM) and binary arithmetic encoding (BAE). The coding engine for CABAC is illustrated in Figure 2.6.

Figure 2.6: CABAC encoding engine [3]

Binarization is a data pre-processing procedure. In the Binarization procedure, non-binary syntax elements are coded into a string of binary symbols called *bins*. An individual binary symbol is referred to as simply a *bin*. There are totally five methods to binarize the input syntax elements. The methods are listed below:

- Table mapping

- Unary coding

- Truncated Unary coding

- Fixed length coding

- Unary Exponential Golomb k-th order (UEG-k) coding

The context modeler computes a context index (ctxIdx) for each bin. This context index is used to find a context model that is stored as the probability state tables. These tables are updated with each bin and reinitialised at the start of each slice.

For the Main profile of the H.264 standard, a total of 399 context models are stored. The context index (ctxIdx) is usually the sum of the context index offset (ctxIdxOffset) and the context index increment (ctxIdxInc). The only exceptions to the above statement is the calculation of the context index for residual syntax elements, where it is the sum of ctxIdxOffset, ctxIdxInc and context block category offset (ctxBlockCatOffset). The ctxBlockCatOffset depends on the context block category of the macroblock presently being encoded.

The ctxIdxOffset is solely determined by the syntax element type and slice type. The ctxIdxInc, however is more complicated and differs for each bin of the coded syntax element. This indicates it is dependent on the index of the bin or bin index (binIdx).

The calculation of the ctxIdxInc is dependent upon neighbor information in some of the cases. For residual syntax elements, the ctxIdxInc calculation also depends upon the scanning position of the current element being coded and upon the number of previously encoded coefficients. The calculations specific to each element are further elaborated in Chapter 4.

Finally each bin value and its corresponding ctxIdx is sent to the Binary Arithmetic encoder. The Binary Arithmetic encoder stores information such as most probable symbol (MPS), and the probability of that state. This consists of the context information that can be accessed with the ctxIdx. In the Binary Arithmetic encoder, there are two possible symbols, namely 0 (zero) and 1 (one). If one of the symbols is the most probable symbol, then the other symbol becomes the least probable symbol (LPS). Typically a memory is employed to store the context information consisting of probability state index and value of most probable state (ranging from 0-399), called context memory or context table.

In arithmetic coding, a coding interval is setup and updated based on the probability of MPS and LPS. The code word of arithmetic coding is generated from recursively dividing the interval. Two variables are used to keep track of the interval. The Low variable and the Range variable. In this implementation they are referred to as codILow and codIRange respectively. The Figure 2.7 shows the Range and Low values and when they are updated.

The initial value of the Range is 510 and it is a 9-bit register. The initial value of the

Figure 2.7: Updating the Range and Low variables in BAE

Low is 0 and it is a 10-bit register. rMPS and rLPS represents the two corresponding sub-intervals of MPS and LPS, respectively. If input bin is equal to MPS, rMPS is chosen as the new interval, otherwise rLPS is selected. When the updated Range is found to lie outside the interval 256 and 511 inclusive, a renormalization procedure is employed. The renormalization procedure is where most of the code word is constructed.

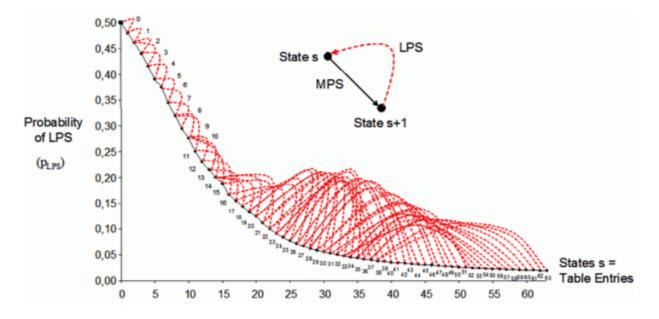

The probability state  $P_{LPS}$  is needed for computing the rLPS value. This value ranges from 0 to 0.5 and it is quantised to 64 discrete probability states. These states are indexed by a variable pStateIdx ranging from 0 to 63. The transition to next state based on the current bin is shown in Figure 2.8. Hence a table look up is used instead of multiplication to update the probability state.

Another multiplication operation in this stage, the computation of rLPS = Range \*  $R_{LPS}$ , is also converted to a table lookup. The Range is quantized to four  $R_Q$  values. The product rLPS is also quantized to 256 values based on  $R_Q$  and pStateIdx. As a result, computing of rLPS can be simply done by looking up in a two-dimension table, in which R Q and pStateIdx are the two indices.

The other two coding methods are elaborated below. The first one is the Bypass coding engine. In this engine, the context modeler stage is bypassed. This means that the previous values

Figure 2.8: Updating the Range and Low variables in BAE

of Range and Low are used and the renormalization for the bypass method is invoked. In the bypass coding engine the probability of the two symbols is considered to be equal to 0.5.

The second alternative coding engine, namely the terminate coding engine, is invoked when the end\_of \_slice syntax element is encountered or when the mb\_type is of the IPCM variety. Here also no context model is chosen. The LPS is fixed to 1 and the rLPS is fixed to 2. Otherwise, the renormalization is the same. When the end of a slice is encountered, then there is also a flushing algorithm that is called.

Every time a new slice begins, an initialize algorithm is invoked which resets all the 399 context models, based on the slice type and the cabac\_init\_idc value. The slice\_QP variable is used to compute the exact context.

#### 2.2.2 Syntax elements

The CABAC coding process uses a total 18 different types of syntax elements which, based on the carried semantics, are divided into 5 categories. This section explains the semantics specified by each syntax element.

**mb\_type** specifies the type of macroblock. The macroblock type in I slice is specified based on the partition scheme of the macroblock in intra prediction. In B slice and P slice, the macroblock

| Category                                                                             | Syntax Element               |  |  |

|--------------------------------------------------------------------------------------|------------------------------|--|--|

|                                                                                      | mb_type                      |  |  |

| Category<br>Macroblock type<br>Inter Prediction<br>Intra Prediction<br>Residual Data | sub_mb_type                  |  |  |

| Inter Duadiation                                                                     | mvd_lX                       |  |  |

|                                                                                      | ref_idx_lX                   |  |  |

|                                                                                      | $intra_chroma_pred_mode$     |  |  |

| Intra Prediction                                                                     | prev_intra4x4_pred_mode_flag |  |  |

|                                                                                      | rem_intra4x4_pred_mode       |  |  |

|                                                                                      | $coded\_block\_pattern$      |  |  |

|                                                                                      | coded_block_flag             |  |  |

| Pagidual Data                                                                        | significant_coeff_flag       |  |  |

| Residual Data                                                                        | last_significant_coeff_flag  |  |  |

|                                                                                      | coeff_abs_level_minus1       |  |  |

|                                                                                      | coeff_sign_flag              |  |  |

|                                                                                      | $mb_qp_delta$                |  |  |

| Control flags and parameters                                                         | mb_field_coding_flag         |  |  |

|                                                                                      | mb_skip_flag                 |  |  |

|                                                                                      | end_of_slice_flag            |  |  |

Table 2.1: Syntax element categories for CABAC

type is based on both partition scheme and inter prediction mode of this macroblock.

sub\_mb\_type specifies sub-macroblock type. The sub-macroblock is only used in the case of B slice and P slice. The sub-mb type is based on both partition scheme and inter prediction mode of this sub-macroblock.

**mvd\_lX\_[mbPartIdx][subMbPartIdx][compIdx]** motion vector difference (MVD) is the difference between the motion vector component and its prediction during the process of motion estimation. The value X in mvd lX can be either 0 or 1, designating the reference list used in prediction. list 0 is used for backward prediction and list 1 for forward prediction. mbPartIdx

specifies the index of macroblock partition and subMbPartIdx specifies the index of sub-macroblock partition. compIdx specifies the motion vector component index. For horizontal vector, it is assigned 0 and 1 for vertical vector. The horizontal and vertical MVD are considered to be two separate types of syntax elements.

**ref\_idx\_IX[mbPartIdx]** specifies the index of the reference picture in the reference list for motion estimation. The X in ref idx IX is the same as the X in MVD. mbPartIdx is the index of the macroblock partition.

intra\_chroma\_pred\_mode (ICPM) specifies the intra prediction mode for chroma information inside a macroblock.

prev\_intra4x4\_pred\_mode\_flag and rem\_intra4x4\_pred\_mode specify intra 4x4 prediction mode for each 4x4 luma block. prev\_intra4x4\_pred\_mode\_flag is set to 0 when there is no rem\_intra4x4\_pred\_mode syntax element in the macroblock.

coded\_block\_pattern (CBP) specifies which of the four 8x8 luma blocks and two 8x8 chroma blocks contain non-zero transform coefficients. The four bits for luma blocks in CBP are called CBP-Luma and the two bits for chroma blocks in CBP are called CBP-Chroma.

**coded\_block\_flag (CBF)** is set to 0 when a transform block contains no non-zero transform coefficients. It is set to 1 when the block contains at least one non-zero transform coefficient.

significant\_coeff\_flag[scanningPos] (SCF) is set to 0 when the transform coefficient level at current scanning position is equal to 0. It is equal to 1 when this position has non-zero transform coefficient level value.

last\_significant\_coeff\_flag[scanningPos] (LSCF) is set to 1 when the following scanning positions within this transform block have all zero values. It is set to 0 when there is at least one non-zero transform coefficient value in the following scanning positions.

**coeff\_abs\_level\_minus1[scanningPos]** is the absolute value of the transform coefficient level value minus 1 when his position has non-zero value.

**coeff\_sign\_flag**[**scanningPos**] is the sign of the transform coefficient level value at this position.

**mb\_qp\_delta (QPD)** specifies the difference between the QP used in the current macroblock and the previous macroblock. The QPD of the first macroblock in each slice specifies the difference between the first macroblock QP and the slice QP.

**mb\_field\_coding\_flag** is set to 0 when current macroblock pair is a frame coding macroblock pair, and 1 when it is field coding macroblock pair.

mb\_skip\_flag indicates if current macroblock is skipped or not.

end\_of\_slice\_flag this is set to 0 when this macroblock is not the final macroblock in a slice, is set to 1 when it is the final macroblock of a slice. This is always the final syntax element within the macroblock.

## Chapter 3

# The KiloCore Many-Core Processor Array Architecture

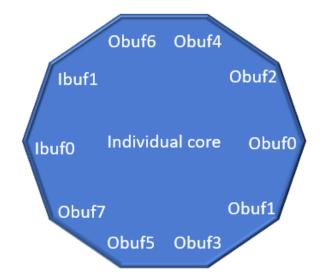

The body of work that is this thesis, describes the implementation of the Context-based Adaptive Binary Arithmetic Coder on the KiloCore II platform. The KiloCore II is a large array of independent, programmable, single issue, RISC-type processors [4]. Each processor has its own memory module and there are multiple big memory modules on the chip that have dual access to the last row of the processors. A single processor can fan out to up to 8 other independent processors. Although this work was implemented on a fourth-generation KiloCore II architecture, the third-generation KiloCore architecture is functionally identical for the purposes of this work. Thus, this chapter will provide the salient features of the KiloCore architecture and chip.

#### 3.1 Processors

Each processor contains a 128x40-bit instruction memory, 512 Bytes of data memory, three programmable data address generators, two 32x16-bit input buffers, and a 16-bit fixed-point datapath with a 32-bit multiplier output and a 40-bit accumulator. The 72 instruction types include signed and unsigned operations to enable efficient scaling to 32 bit or larger word widths, with no instructions being algorithm-specific. Processors support predication for any instruction using two conditional execution masks, static branch prediction, and automated hardware looping for accelerating inner loops.

Each processor issues one 40-bit instruction in-order per cycle into its seven-stage pipeline

as shown in Figure 3.1.

Figure 3.1: KiloCore pipeline [4]

#### 3.2 Memory

Independent memory modules each contain a 64-kByte SRAM and are shared between two neighboring processors. Modules support random and a variety of programmable burst access patterns for data reading and writing, and are also capable of streaming instructions for largeprogram execution to an adjoining processor using an internal control module. When executing an instruction stream from an independent memory, a processor transfers program control and branch prediction control to dedicated circuits inside the memory block to more efficiently execute across branches. Each memory module contains two 32x18-bit input buffers, two 32x16-bit output buffers, and one 16x2-bit processor response buffer, and supports 28.4 Gb/s of I/O bandwidth.

#### 3.3 Communication between processors

The processor array connects processors and independent memories via a 2-D mesh, a topology which maps well to planar integrated circuits and scales simply as the number of processors per die increases. Communication on-chip is accomplished by two comple- mentary means: a very high throughput and low-latency circuit-switched network and a very-small-area packet router. The circuit-switched links are source-synchronous, so the source clock travels with the data to the destination, where it is translated to the destination-processors clock domain. The network supports communication between ad- jacent and distant processors, as resources allow, with each link supporting a maximum rate of 28.5 Gb/s with optionally inserted registers to maintain data integrity over long distances. Each of the four edges of each processor has two such links entering and two links exiting the processor. The high-throughput circuit-switched network is especially efficient transferring data to an adjacent processor, dissipates 59% less energy than writ- ing and later reading that data using local data memory, and transferring that data to a processor four tiles away requires only 1% more energy than using local data memory. The packet router inside each processor occupies only 9% of each processors area and is especially effective for high fan-in and high fan-out communication, as well as for admin- istrative messaging. Each router supports 45.5 Gb/s of throughput with a maximum of 9.1 Gb/s per port. Routers operate autonomously from their host processors and contain their own clock oscillators, so they can power down to zero active power when there are no packets to process. Each router contains five 4x18-bit input buffers, one for each cardinal direction and one for the local processor. Routers utilize wormhole routing to efficiently transfer long data bursts, in which a header packet will reserve a path and is followed by an arbitrary number of data packets, terminating in a tail packet which releases the path.

The clocking system in the KiloCore is governed by a Globally Asynchronous Locally Synchronous (GALS) clocking style, which separates processing blocks such that each part is clocked by an independent clock domain [12].

## 3.4 Project Manager

The Project Manager provides support for writing task parallel applications for the KiloCore I/II style of many-core array, preparing applications to run on a target architecture, and launching simulations to verify correctness and gather measurements. Apps are set up by a python script that will import and apply the various Project\_Manager functions and classes.

An Application object is the basic repository for all application information, including user defined setup, annotations and simulation results. Tasks are defined which make up the compute part of the application. Common tasks include Processor, Memory, Input\_Handler, Output\_Handler. Links between cores connect indexed output ports to indexed input ports of the tasks. Links include Circuit\_Link, Memory\_Link, and Packet\_Link. Input source files need to added to the project. Code files may be C++ (to be compiled to assembly) or simulator formatted assembly. Data files provide test input data or reference output data, with some optional formatting support to translate them into the expected data width of the architecture.

The Asap3 and Asap4 arrays have been predefined architecture targets in the Project Manager. Simulator related options are also accessible. Finally transforms are run to get analysis information of the application like simulation time, throughput, energy, branch accuracy, utilization information and if applied, simulation reference accuracy.

# Chapter 4

# Methodology

### 4.1 Overview

The implementation of CABAC on the AsAP array involved breaking up the algorithm into smaller tasks that could be performed independently of the other tasks.

Figure 4.1: CABAC data flow

The grey boxes represent a block within the CABAC. The white parallelogram-shaped boxes represent the variables that are processed by the grey boxes. These variables are either inputs

Figure 4.2: Representation of a single core's ports.

to the system or processed outputs.

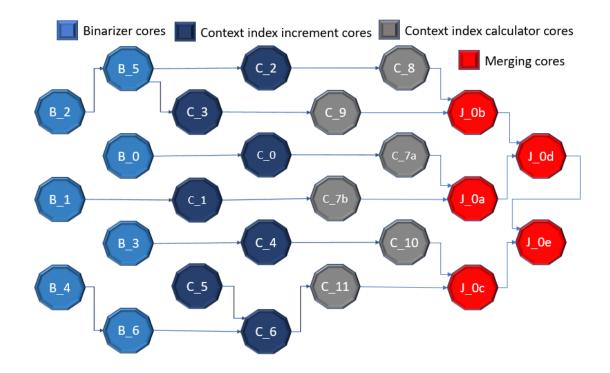

The flow of bits starts at the input handling cores. These cores process the input that is received by the JM software. These cores are also responsible for fanning out the syntax element information to the binarizer cores. All the binarizer cores have their own context index increment cores as well as context index calculator cores.

Two context index calculator cores connect to a single bin accumulator core which fans in the data for further processing. There are three stages of the bin accumulator cores. The purpose of fanning in at this stage is due to the fact that all the cores have to access the same set of context tables. This brings us to the last section of the CABAC algorithm which is the Binary Arithmetic encoder.

The Binary Arithmetic encoder (BAE) takes in all the bins associated with a single syntax element, and processes each bin individually, updating the context tables after each bin. The last function of the BAE block is the renormalization and symbol count updating. The BAE block is also responsible for packing the bits into words of 16 bits. The output written to a text file consists is the bin stream of the words that were produced by the last stage of the BAE.

This chapter elaborates the working of the implementation starting with the input handling and discussing each block of the CABAC algorithm. The representation of a core will look like Figure 4.2. The color representation for each block is given in Figure 4.3.

Figure 4.3: Colors of various stages of cores

#### 4.1.1 Input data handling

The input handling cores receive input from the JM software. Each line of the input represents one syntax element. The Table 4.1 shows the data that is received for each syntax element.

| 1. | Initialise enable signal        | 9.  | Intra Chroma Pred Mode for B and A  |

|----|---------------------------------|-----|-------------------------------------|

| 2. | Syntax element value            | 10. | Motion vectors for B and A          |

| 3. | Syntax element type             | 11. | ref_idx_lX for B and A              |

| 4. | Indices of x and y coordinates  | 12. | mb_type for B and A                 |

| 5. | List variable for ref_idx_lX    | 13. | Prediction direction for ref_idx_lX |

| 6. | Variable ctxBlockCat            | 14. | mbSkip flags for B and A            |

| 7. | Coded block flag                | 15. | mbField flags for B and A           |

| 8. | Coded block pattern for B and A | 16. | mbAvailable flags for B and A       |

Table 4.1: Input variables from JM software

Not all the values received for each syntax element is relevant information. The input information is distributed to more specific cores in the *slice\_mb\_storage* cores. These extract the relevant data for each element and pass it on to specific context modeling cores.

This subsection elaborates on the working of the following cores:

- I\_0 *input\_reader*: uses one input port and five output ports.

- I\_1 *input\_slice*: uses one input port and one output port.

- I\_2 *bin\_distributor*: uses both input ports and six output ports.

- I\_3 *slice\_mb\_storage*: uses both input ports and one output port.

- I\_4 *slice\_mb\_storage\_2*: uses one input port and four output ports.

The CABAC implementation on KiloCore II has two external input handlers. The first handler named *input\_reader* is utilised for the Syntax Element information and the second one named *input\_slice* is used for the Slice information.

Figure 4.4: Complete input and output connections of the core *bin\_distributor*(I\_2). I\_0: *input\_reader*, I\_1: *input\_slice*, I\_3: *slice\_mb\_storage*, B\_0 to B\_4: binarizer cores

The *input\_reader* core also deals with processing the neighbor information that it receives along with the Syntax Element data. The *input\_reader* core has three output circuit links connected to context index increment calculating cores discussed in 4.3. Another output link is connected to the core, *bin\_distributor*, that is responsible for collecting the syntax element information and the slice information from the *input\_slice* core and passing it forward to the binarizer cores, which are *binarizer\_mbtypeIP*, *binarizer\_mbtypeB*, *binarizer\_submbtype\_fixed*, *binarizer\_tunary* and *binarizer\_uegk*. The Figure 4.1 shows the connections to the *bin\_distributor*.

Figure 4.5: Complete input and output connections of the core *input\_reader* (I\_0) and *slice\_mb\_storage* (I\_3). I\_2: *bin\_distributor*, C\_0: *ctxIdxInc\_mbtype*, C\_1: *ctxIdxInc\_fixed*, C\_2: *ctxIdxInc\_blockcat*, C\_3: *ctxIdxInc\_tunary*, C\_4: *uegk\_parser*

The last output circuit link goes to *slice\_mb\_storage* core, which stores the relevant information about the current slice and current macroblock. The *slice\_mb\_storage* core is also responsible for parsing neighbor information like the *input\_reader* core. Hence, it also has output links to context index increment calculator cores. The Figure 4.2 shows the input and output connections for *input\_reader* and *slice\_mb\_storage* cores.

The macroblock information that the *slice\_mb\_storage* core stores includes values of syntax elements that have a set value for the given macroblock. The syntax elements in question are the

mb\_type, mb\_skip\_flag, sub\_mb\_type, mb\_field\_decoding\_flag, mb\_qp\_delta. It is also responsible for maintaining the scanning position, numLevelGt1, numLevelEq1 counters. These counters are required in the encoding of Residual syntax elements.

The slice information it stores is the slice\_type, frame\_coded\_flag, MBaffFrameFlag, slice\_QP and cabac\_init\_idc.

## 4.2 Binarizer

Each binarizer core deals with one or more method of converting the syntax elements into bins, as specified by the standard [5], based on the syntax element type. The algorithms for doing that are elaborated in this section.

The Binarizer consists of the following cores:

- B\_0 *binarizer\_mbtypeIP*: uses one input port and one output port.

- B\_1 *binarizer\_mbtypeB*: uses one input port and one output port.

- B\_2 binarizer\_submbtype\_fixed: uses one input port and one output port.

- B<sub>-3</sub> binarizer\_tunary: uses one input port and one output port.

- B\_4 *binarizer\_uegk*: uses one input port and one output port.

- B\_5 *sub\_mb\_type\_table*: uses one input port and two output ports.

- B<sub>-6</sub> uegk: uses one input port and one output port.

The input to this section is the syntax element value, the syntax element type and the slice type.

The output consists of the bins created, ctxIdxOffset for each type of syntax element, the length of the bins and the length of the suffix word, if that is applicable. The ctxIdxOffset for each syntax element is elaborated in Table 4.2. The binarizer core that processes each syntax element is also mentioned in Table 4.2. [3]

For the mb\_type syntax element part of the P and B slices, the ctxIdxOffset is assigned based on whether the bin index is part of the prefix or suffix. The ctxIdxOffsets for the significant\_coeff\_flag and last\_significant\_coeff\_flag change depending on whether it is field coding or frame coding.

| Syntax Element type          | Slice type | ctxIdxOffset | Binarizer core                |

|------------------------------|------------|--------------|-------------------------------|

| mb_type                      | Ι          | 3            | $binarizer\_mbtypeIP$         |

| mb_type                      | Р          | 14/17        | $binarizer\_mbtypeIP$         |

| mb_type                      | В          | 27/32        | $binarizer\_mbtypeB$          |

| mb_skip_flag                 | Р          | 11           | $binarizer\_submbtype\_fixed$ |

| mb_skip_flag                 | В          | 24           | binarizer_submbtype_fixed     |

| sub_mb_type                  | Р          | 21           | $binarizer\_submbtype\_fixed$ |

| sub_mb_type                  | В          | 36           | binarizer_submbtype_fixed     |

| mvd_l0                       | all        | 40           | $binarizer\_uegk$             |

| mvd_l1                       | all        | 47           | $binarizer\_uegk$             |

| ref_idx_lX                   | all        | 54           | $binarizer\_tunary$           |

| $mb_qp_delta$                | all        | 60           | $binarizer\_tunary$           |

| $intra_chroma_pred_mode$     | all        | 64           | $binarizer\_tunary$           |

| prev_intra4x4_pred_mode_flag | all        | 68           | $binarizer\_submbtype\_fixed$ |

| rem_intra4x4_pred_mode       | all        | 69           | binarizer_submbtype_fixed     |

| mb_field_coding_flag         | all        | 70           | binarizer_submbtype_fixed     |

| $coded_block_pattern$        | all        | 73           | binarizer_submbtype_fixed     |

| coded_block_flag             | all        | 85           | binarizer_submbtype_fixed     |

| significant_coeff_flag       | all        | 105/277      | binarizer_submbtype_fixed     |

| last_significant_coeff_flag  | all        | 166/338      | binarizer_submbtype_fixed     |

| abs_coeff_level_minus1       | all        | 227          | $binarizer\_uegk$             |

| coeff_sign_flag              | all        | 0            | binarizer_submbtype_fixed     |

| end_of_slice_flag            | all        | 276          | binarizer_submbtype_fixed     |

Table 4.2: Values of ctxIdxOffset for each syntax element type

As previously mentioned in the input handling section, the *bin\_distributor* core sends the syntax element and slice information to all the binarizer cores. Of these cores, the *binarizer\_submbtype\_fixed* and *binarizer\_uegk* ones are connected to the *sub\_mb\_type* and *uegk* cores respectively. The reason for this is to spilt these binarization function to fit into 128 instructions available in each core.

#### 4.2.1 Tabular lookup coding

The syntax elements that use tabular lookup coding are the mb\_type and sub\_mb\_type. The tables are divided based on the macroblock type, whether it is I type, P type or B type. When the macroblock is P or B type, there is also a suffix that is added to the coded word based on the syntax value. These tables have the length of the bins stored in the tables. The maximum length of the bins is 13, which is fewer bits than the size of a word in the KiloCore Architecture [4].

#### Syntax Element mb\_type

The mb\_type syntax element has 26 values for the I macroblock, 31 values for the P macroblock, 25 of which have a suffix and 49 values for the B macroblock, again 25 of which have a suffix.

The bins of the I and P macroblocks are stored in tables in the *binarizer\_mbtypeIP* core. The bins of the B macroblock are stored in the *binarizer\_mbtypeB* core.

#### Syntax Element sub\_mb\_type

The sub\_mb\_type syntax element only appears in P and B macroblocks. There are 4 table entries for the P macroblock and 13 entries for the B macroblock.

The tabular lookup coding for the sub\_mb\_type syntax element is split across two cores, namely the *binarizer\_submbtype\_fixed* and the *sub\_mb\_type\_table*. The first core mainly deals with the syntax elements that have fixed length coding discussed in subsection 4.2.2. The second core has the tabular values for the sub\_mb\_type.

#### 4.2.2 Fixed Length coding

The syntax elements that follow the fixed length coding are:

- mb\_skip\_flag,

- prev\_intra4x4\_pred\_mode\_flag,

- rem\_intra4x4\_pred\_mode,

- mb\_field\_coding\_flag,

- coded\_block\_pattern,

- coded\_block\_flag,

- significant\_coeff\_flag,

- last\_significant\_coeff\_flag,

- end\_of\_slice\_flag,

- coeff\_sign\_flag.

The syntax element coded\_block\_pattern follows both the fixed length coding for the lower four bits and truncated unary coding for the upper two bits, which is explained further in subsection 4.2.4. All these above mentioned syntax elements are dealt with in the *binarizer\_submgtype\_fixed* core.

The fixed length has a variable cmax which determines the length of the coded bins. The formula for finding the length from cmax is:

$$length = \lceil log_2(cmax+1) \rceil \tag{4.1}$$

The rem\_intra4x4\_pred\_mode syntax element has cmax value equal to 7. The lower four bits of the syntax element coded\_block\_pattern has a value of cmax equal to 15. The remaining syntax elements that follow fixed length coding all have the fixed length of 1. All the syntax elements of this type produce bins that can easily fit in a single word of the KiloCore. [13]

For the elements that have cmax equal to 1, it is a matter of simple assignment to get the coded bin. The elements with higher cmax follow a method of bit shifting shown in Equation 4.2.

$$bins = \sum_{i=0}^{length-1} ((SE_val >> (length - (i+1)))\&1) << i$$

(4.2)

An example of fixed length coding is shown in Table 4.3

| Syntax Element value | Fixed length coded bins |

|----------------------|-------------------------|

| 1                    | 100                     |

| 2                    | 010                     |

| 3                    | 110                     |

| 4                    | 001                     |

| 5                    | 101                     |

| 6                    | 011                     |

| 7                    | 111                     |

Table 4.3: Example of fixed length coding when cmax = 7 [6]

#### 4.2.3 Unary coding

The syntax elements that follow the unary coding are ref\_idx\_lX, mb\_qp\_delta. These are handled in the *binarizer\_tunary* core.

In the unary coding method, the bins produced include SE\_val number of ones followed by a zero. Thus, the syntax element value determines the length of the bins, given by Equation 4.3.

$$length = SE\_val + 1 \tag{4.3}$$

The range of values of the ref\_idx\_IX syntax element is 0 to 31 inclusive. The maximum length of the bins coded is thus 32.

The range of values that the syntax element mb\_qp\_delta can take is from -26 to 25. The values associated with this syntax element are first mapped to unsigned values [1] ranging from 0 to 52 inclusive before the unary coding method is applied. That makes the maximum length of the bins coded to be 53.

The size of a word in the KiloCore is 16 bits [4]. Therefore, we need a total of four words to fully represent the bins produced by this coding technique. This is the first binarization coding method where we encounter bins larger than a single word in the KiloCore.

The mapping of the signed values of the mb\_qp\_delta elements is governed by Equation 4.4

that is shown here.

$$map\_value = \begin{cases} (SE\_val << 1) + 1, SE\_val > 0 \\ |SE\_val| << 1, SE\_val < 0 \\ 0, otherwise \end{cases}$$

(4.4)

## 4.2.4 Truncated unary coding

The syntax elements using the truncated unary method are intra\_chroma\_pred\_mode, coded\_block\_pattern, and prefixs of mvd\_l0, mvd\_l1 and abs\_coeff\_level\_minus1. These elements are handled in *binarizer\_tunary*, *binarizer\_submbtype\_fixed* and *binarizer\_uegk* cores.

The truncated unary method is very similar to the unary coding method. The difference is that for syntax elements having values greater than a variable cmax get truncated to cmax number of bits. This code word consists of cmax number of ones.

| The | cmax | values | for | all       | the | syntax | elements | encoded | in  | this  | manner | is | listed i | n   | Table 4.5. |

|-----|------|--------|-----|-----------|-----|--------|----------|---------|-----|-------|--------|----|----------|-----|------------|

| THE | сшал | varues | 101 | $a_{\Pi}$ | one | Symuan | elements | encoueu | 111 | 01115 | manner | 12 | insteu i | .11 | Table 4.0. |

| Syntax Element type           | cmax for Truncated unary coding |

|-------------------------------|---------------------------------|

| intra_chroma_pred_mode        | 3                               |

| coded_block_pattern prefix    | 2                               |

| mvd_l0 prefix                 | 9                               |

| mvd_l1 prefix                 | 9                               |

| abs_coeff_level_minus1 prefix | 14                              |

Table 4.4: cmax values for truncated unary coding

The bins, length and ctxIdxOffset of the Syntax elements are forwarded to the next section of context modeler cores.

## 4.2.5 Unary Exponential Golomb k-th order coding

The syntax elements that Unary Exponential Golomb k-th order coding (UEGk) are mvd\_l0, mvd\_l1 and abs\_coeff\_level\_minus1. These are dealt with in the *binarizer\_uegk* and *uegk* cores.

| Syntax Element type    | k | uCoff | signedValFlag | Range             |

|------------------------|---|-------|---------------|-------------------|

| mvd_l0                 | 3 | 9     | 1             | [-2048, 2048)     |

| mvd_l1                 | 3 | 9     | 1             | [-512, 512)       |

| abs_coeff_level_minus1 | 0 | 14    | 0             | $[0, 2^{15} - 1]$ |

The parameters associated with the UEGk coding are shown in Table 4.4. These values are initialised in the *binarizer\_ueqk* core. The computation of the bins is done in the *ueqk* core.

Table 4.5: Parameters for UEGk coding

As already stated in 4.2.4, the prefix for these syntax elements are coded using the Truncated coding method. The process of coding the syntax element prefix is detailed in Algorithm 1.

The suffix of the Syntax elements coded using the UEGk method is more complicated than the prefix. Whether the incoming syntax element is positive or negative is to be considered for the coding. A variable called sufS is made use of in the calculation. The size of sufS is determined based on the range of values of the syntax element. The ranges of mvd\_l0, mvd\_l1, abs\_coeff\_level\_minus1 are given in Table 4.5.

#### Algorithm 1 Prefix of UEGk coding

if SE\_val is less than uCoff then

Assign prefix equal to SE\_val number of bits all equal to 1 followed by bit 0;

else

Assign prefix equal to uCoff number of bits all equal to 1;

end

if signedValFlag is equal to zero and SE\_val is less than uCoff or signedValFlag is equal to 1 and

prefix is equal to 0 then

| Output is equal to only prefix;

end

From the ranges table, it can be determined that the maximum size of prefix for mvd\_l0 and mvd\_l1 is 9 and maximum size for prefix of abs\_coeff\_level\_minus1 is 14. The maximum size of suffix for mvd\_l0 and mvd\_l1 is 19 bits and the maximum size of suffix for abs\_coeff\_level\_minus1 is 29 bits. This means that the variable sufS has be larger than 29 bits. In the KiloCore II architecture, the int32\_t register is used for the purpose.

The complete algorithm for coding the suffix is detailed in Algorithm 2.

```

Algorithm 2 Suffix of Unary Exponential Golomb kth-order coding

Reset signFlag to 0;

if SE_val is less than zero then

Set signFlag to 1;

Assign the absolute value of SE_val to SE_val;

end

Initialize suffix to be 0;

if SE_val is greater than or equal to uCoff then

Assign the difference betwenn SE_val and uCoff to sufS;

Initialize stoploop to be 0;

while stoploop is not equal to 1 do

if sufS is greater than or equal to 2^k then

Add bit 1 to right end of Suffix;

Subtract 2^k from sufS;

Increment k;

end

else

Add bit 0 to right end of suffix;

while value of k decremented by 1 is not equal to zero do

Shift sufS to the right k times;

Addend the least significant bit of the shifted value to the right end of suffix;

end

Set stoploop to equal 1;

end

end

end

```

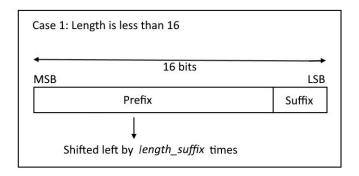

The maximum length of the bins produced is 43 bits. The bins produced is divided into three 16 bit words, because the coded word will not fit in even the 32-bit register available. The prefix bits must occupy the most significant bits of the first 16-bit word sent to the next core.

Three cases are formed for the division of the prefix and suffix into the three 16-bit registers.

The first case is when all the bits will fit into a single word. This condition is satisfied only when length of suffix is less than difference between 16 and the length of prefix. In this case we shift the prefix bits to the left by length of suffix and bit wise OR is performed between the shifted prefix and the suffix. Figure 4.5 shows the register in this case.

Figure 4.6: Prefix and Suffix words in 16-bit register: Case 1

Figure 4.7: Prefix and Suffix words in 16-bit register: Case 2

The second case is when the total length is less than 32 bits, this means that two registers are sufficient to store the complete word. In this case, the first word contains the prefix shifted to the left by total length of register (16) - length of prefix bits. The remaining bits are occupied by the most significant bits of the suffix. So, the suffix is shifted right by length of suffix - (total register length - length of prefix). The second 16 bit word has the remaining suffix bits. A mask is constructed of the remaining length of the suffix. A bit-wise AND operation is performed between this mask and the suffix.

The last case is the one where the length of the coded word is larger than two registers. The shifting for the first 16-bit register is the same as the second case. The prefix bits shifted to the leftmost and the remaining bits are made up of the most significant suffix bits.

Figure 4.8: Prefix and Suffix words in 16-bit register: Case 3

The second word consists of the middle part of the suffix. We can be certain that the prefix will not extend to this word, since the maximum length of the prefix is 14. The middle of the suffix is got by shifting out the right most bits of the suffix that should appear in the third word. So the suffix is shifted right by length of the suffix subtracted by how much was in the first word and by how much should be in the second word, which is the full size of the word, that is 16.

$$shift\_value = length\_suffix - (16 - length\_prefix) - 16$$

$$(4.5)$$

The shift value is given by the Equation 4.5. The middle word should also masked in order to remove the left most bits that would have been part of the first word. So the shifted suffix and a mask of sixteen ones are inputs to a logical AND gate.

The third word is the remaining bits of the suffix. The suffix and a mask of length

shift\_value given in 4.5 are applied to a bit-wise AND gate to get the remaining bits.

When there is a SE\_type is a signed value, it is coded as shown below in Algorithm 3.

Algorithm 3 Sign bit of UEGk coding

if signedValFlag is equal to 1 and SE\_val is not equal to zero then

if signFlag is equal to 0 then

| Add bit 0 to the right end of suffix;

else

| Add bit 1 to the right end of suffix;

end

end

Once the prefix, suffix and sign bit are correctly coded into bins, the bins, along with the length of the full word and the length of suffix are forwarded to the next section.

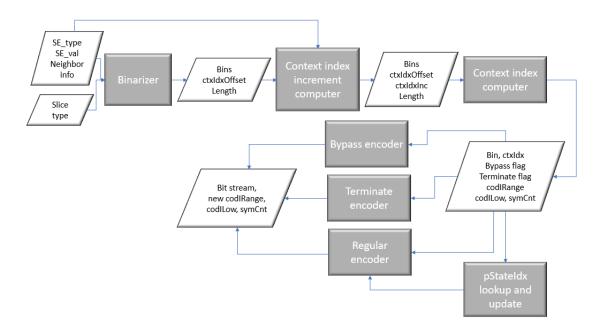

# 4.3 Context Modeler

The context modeler is explained in this subsection. Figure 4.9, shows the flow of the information in the block. As can be seen in Figure 4.9, for each bin of the bins produced, there is a ctxIdxInc and ctxIdx generated. The same ctxIdxOffset is assigned for each set of bins produced. The ctxIdxBlockOffset is based on the ctxIdxBlockCat. This is further elaborated in the subsection 4.3.2.

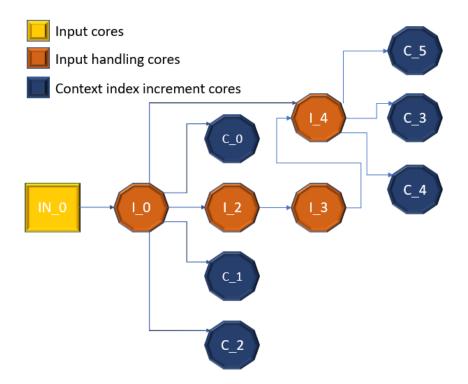

The context modeler requires the following cores:

- C\_0 ctxIdxInc\_mbtypeIP: uses both input ports and one output port.

- C\_1 *ctxIdxInc\_mbtypeB*: uses both input ports and one output port.

- C\_2 *ctxIdxInc\_fixed*: uses both input ports and one output port.

- C\_3 *ctxIdxInc\_blockcat*: uses both input ports and one output port.

- C\_4 *ctxIdxInc\_tunary*: uses both input ports and one output port.

- C<sub>5</sub> uegk\_parser: uses one input port and one output port.

- C\_6 *ctxIdxInc\_uegk*: uses both input ports and one output port.

Figure 4.9: Flowchart of the Context modeler block

- C\_7 *ctxIdx\_mbtype*: uses one input port and one output port.

- C\_8 ctxIdx\_fixed: uses one input port and one output port.

- C\_9 ctxIdx\_blockcat: uses one input port and one output port.

- C\_10 ctxIdx\_tunary: uses one input port and one output port.

- C\_11 ctxIdx\_uegk: uses one input port and one output port.

- J\_0 *bin\_join*: uses both input ports and one output port.

The input to this block is the ctxIdxOffset, the bins generated by the binarizer cores, the length of the bins and the suffix. The relevant neighbor information is also passed on as input to this block. While the bins and associated information are passed to the context index increment cores through the binarizer cores, the neighbor information is sent from the input handling cores, *input\_reader* and *slice\_storage\_2*. The output of this block is the context index (ctxIdx), the bins to be encoded and the length of the bins.

Figure 4.10: Connections for the Context modeler block.  $B_0$  to  $B_6$  are the binarizer block cores.  $C_0$  to  $C_5$  are the context index increment cores.  $C_6$  to  $C_{10}$  are the context index calculator cores.  $J_0$  cores are the *bin\_join* cores.

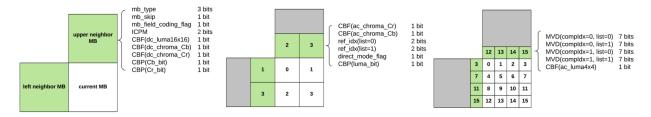

The first section of the Context modeler is the calculation of the context index increment (ctxIdxInc) based on the context index offset (ctxIdxOffset). The ctxIdxInc is computed based on neighbor partition information in the case of mvd\_l0, mvd\_l1, coded\_block\_pattern and ref\_idx\_lX syntax elements. The residual syntax elements, that is coded\_block\_flag, significant\_coeff\_flag, last\_significant\_coeff\_flag and abs\_coeff\_level\_ minus1 all make use of the scanning position of the present macroblock to compute the ctxIdxInc. The syntax elements mb\_type, mb\_skip\_flag, sub\_mb\_type, mb\_qp\_delta, intra\_chroma\_pred\_mode, mb\_field\_decoding\_flag all rely on A and B neighbor information in order to compute the ctxIdxInc. The A and B neighbors are shown in diagram below.

Once the ctxIdxInc is computed the ctxIdx is calculated using this and ctxIdxOffset and in some cases the value of ctxIdxBlockCat.

Each method is detailed in the subsections below. Connections for the context modeler cores is shown in Figure 4.10

#### 4.3.1 Context index increment computation cores